# A 0.3-V 8.5- $\mu$ A Bulk-Driven OTA

Andrea Ballo<sup>®</sup>, Alfio Dario Grasso<sup>®</sup>, Salvatore Pennisi<sup>®</sup>, and Giovanni Susinni

Abstract—A bulk-driven operational transconductance amplifier (OTA) suitable for ultralow-power and ultralow-voltage applications is described. The amplifier exploits local positive feedback in the first stage to increase its transconductance. The OTA entails a single Miller capacitor for frequency compensation, thus saving area occupation and improving frequency performance. As a distinctive feature of the proposed solution, the OTA is stable for capacitive loads higher than 5 pF. Implemented in a 65-nm standard CMOS technology, the proposed solution occupies an area of  $10.6 \cdot 10^{-3}$  mm² and is powered from 0.3 V, with a total quiescent current equal to  $8.5~\mu$ A. Experimental measurements show a gain–bandwidth (GBW) product of 1.65 MHz (0.81 MHz) with a phase margin (PM) equal to  $70^{\circ}$  ( $71^{\circ}$ ) when driving a 50-pF (150-pF) load, featuring the best figures of merit compared to other multistage sub-1-V OTAs in the literature.

*Index Terms*— Bulk-driven, CMOS analog integrated circuits, low-voltage, operational transconductance amplifier (OTA).

#### I. INTRODUCTION

A major trend in the current electronics industry is the extension of battery life in portable devices through the adoption of ultralow-power design techniques. This has reinforced interest in the development of low-voltage, low-current design approaches. By limiting power consumption is in fact possible to reduce the size of the battery (and consequently the overall volume of the device), thus ensuring the same device lifetime. This latter aspect is especially critical for implanted biomedical devices, where a reduced system volume is desirable to limit invasiveness [1].

Considering CMOS technology, the most widely adopted methodology for enabling analog circuits with low-voltage and low-current capabilities is subthreshold biasing, also known as weak inversion biasing. For example, through this approach, excellent operational transconductance amplifier (OTA) topologies have been implemented [2], [3], [4], [5]. These solutions allow supply voltages from around 1–0.5 V, but with limited input common-mode swing.

When operations below 0.5 V are requested, with rail-to-rail input capabilities, the bulk driving (body driving) technique, even in combination with the subthreshold one, has been proven to be the best solution [6], [7], [8], [9], [10], [11], [12], [13], [14], [15], [16], [17], [18], [19], [20].

To enable bulk driving, the MOSFET gate must be biased to form a conduction channel inversion layer, and the drain current is modulated by varying the bulk voltage through the body effect. In fact, bulk-driven stages allow minimum supply with wide input ranges,

Manuscript received 9 January 2023; revised 20 March 2023 and 8 April 2023; accepted 10 April 2023. Date of publication 25 April 2023; date of current version 25 August 2023. This work was supported by the European Union (NextGeneration EU), through the Ministero dell'Università e della Ricerca (MUR)-Pinao Nazionale di Ripresa e Resilienza (PNRR) project Sicilian MicronanoTech Research And Innovation Center (SAMOTHRACE) under Grant ECS00000022. (Corresponding author: Alfio Dario Grasso.)

Andrea Ballo, Alfio Dario Grasso, and Salvatore Pennisi are with the Dipartimento di Ingegneria Elettrica Elettronica e Informatica (DIEEI), University of Catania, I-95125 Catania, Italy (e-mail: andrea.ballo@unict.it; alfiodario.grasso@unict.it; salvatore.pennisi@unict.it).

Giovanni Susinni is with Eda Industries S.P.A., 95121 Catania, Italy.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TVLSI.2023.3266806.

Digital Object Identifier 10.1109/TVLSI.2023.3266806

including rail-to-rail, and are particularly effective under very low-voltage supply, where the forward biasing of the body-source junction cannot exceed 0.4 V, thus limiting the forward body current in the range of a few picoamperes. However, compared with conventional gate-driven circuits, body-driven counterparts are characterized by lower voltage gain and/or gain-bandwidth (GBW) product, because of the limited value of bulk transconductance,  $g_{\rm mb}$ , which is only about 10%–20% of the gate transconductance,  $g_m$  [21].

To overcome some of these limitations usually found in a conventional body-driven OTA, we present in this brief, a novel three-stage OTA. The main features of the proposed circuit can be summarized as follows.

- It exploits local positive feedback within the first stage to improve its equivalent transconductance.

- 2) Three cascaded gain stages are adopted to further increase the dc gain, and unlike previous solutions, a single Miller capacitor is successfully exploited to implement frequency compensation, thus reducing the overall area occupation and maximizing GBW under a given standby current.

- Class AB operation of the last stage increases slew rate (SR) performance and current driving capability.

- A better common-mode rejection ratio (CMRR) with respect to a previous similar high-performance solution [10] is also inherently achieved by the proposed topology.

The OTA is designed and fabricated using a standard 65-nm CMOS technology. It can operate under a 0.3-V supply and provides a dc gain around 40 dB. Compared with other sub-1-V experimental solutions in the literature, the proposed one offers significant improvements, especially when considering area occupancy and GBW, reflected in the best figures of merit achieved by a body-driven OTA.

Some preliminary results of the proposed OTA have already been presented by the authors in a national conference [22]. In this work, the theoretical analysis is extended to include the effects for high capacitive loads. Moreover, extensive simulations, including corner and Monte Carlo analysis, and additional experimental results are provided.

#### II. PROPOSED AMPLIFIER

A. Topology, Operating Point, and Large Signal Operation

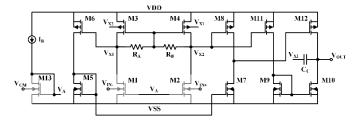

The simplified schematic of the proposed OTA is depicted in Fig. 1. The circuit relies on a bulk-driven nontailed differential pair M1–M2, whose gate voltage,  $V_A$ , is set by M13 and current generator  $I_B$  [10]. Note that transistors M1 and M2 are thick oxide transistors, showing a higher value of the body effect parameter. Transistors M3 and M4 with resistors  $R_A$  and  $R_B$  implement the load of the differential pair. The body and drain terminals of M3 and M4 are cross-coupled as discussed in [23] for a gate-driven OTA. The provided positive feedback increases the differential input stage transconductance, as will appear clear in the following. The bias current of M1–M2 is accurately set by the current mirror ratio  $(W/L)_{1,2}/(W/L)_{13}$  (where W/L is the MOS transistor aspect ratio), provided that the bulk voltage of M1,  $V_{\rm CM}$ , is equal to the common-mode input voltage  $(v_{\rm IN+} + v_{\rm IN-})/2$ .

Considering that no current flows through  $R_A$  and  $R_B$  at dc, the drains of M3-M4 are at the same potential of their gates, i.e., they

Simplified schematic of the proposed OTA.

act as diode-connected transistors. Therefore, transistors M6 and M8 have the same source-gate voltage of M3 and M4, to which we refer to as  $V_{SG}$ . Since the threshold voltage of a pMOS is expressed by

$$V_T = V_{T0} - \gamma \left( \sqrt{2\varphi_F + V_{SB}} - \sqrt{2\varphi_F} \right) \tag{1}$$

where  $V_{T0}$  is the zero-bias threshold,  $\varphi_F$  is the Fermi potential,  $\gamma$  is the body effect parameter, and  $V_{\rm SB}$  is the source-bulk voltage, hence, neglecting the channel length modulation and assuming operation in saturation, and the dc current ratio  $I_{D6.8}/I_{D3.4}$  is

$$\frac{I_{D6,8}}{I_{D3,4}} = \frac{(W/L)_{6,8}}{(W/L)_{3,4}} \left[ 1 - \frac{\gamma \left( \sqrt{2\varphi_F + V_{SG}} - \sqrt{2\varphi_F} \right)}{V_{SG} + V_{TO}} \right]^2 \tag{2}$$

where  $V_{SB} = V_{SG}$  was set for M3 and M4, due to the topological symmetry. As a result, the current mirror ratio in (2) is lower than that of a conventional current mirror, in which the factor in the square brackets equals 1. In other words, if  $(W/L)_{6.8} = (W/L)_{3.4}$  is set,  $I_{D6.8} < I_{D3.4}$  is obtained.

As far as  $I_{D11}$  is concerned, it stands in a current mirror ratio with  $I_{D8}$  and sets the quiescent current in the output stage (M12) through the current mirror M9-M10. Class-AB operation of the last stage is ensured by M11 and M12 for sinking and sourcing output current, respectively.

### B. Small-Signal Analysis

Similar to what was demonstrated in [10], the first stage exhibits a differential output behavior, even though the input voltage is applied only to the bulk of M1 (or equivalently to the bulk of M2). In addition, the differential-mode transconductance of the first stage is enhanced by the positive feedback of the bulk-drain cross-connection of transistors M3 and M4. This can be demonstrated in the same way as was done in [23], which analyzed a gate-driven cross-coupled input stage. The (unbalanced) differential gain of the first stage,  $A_{0,1}$ , is hence given by the equivalent transconductance multiplied by the equivalent output resistance and results to be

$$A_{0,1} = \frac{v_{x1}}{v_{id}} = -\frac{1}{2} G_{\text{mb}} R_{A,B} / r_{o1}$$

$$= -\frac{1}{2} \frac{g_{\text{mb1},2}}{1 - g_{\text{mb3},4} R_{A,B} / r_{o1}} R_{A,B} / r_{o1}$$

(3)

where  $g_{\text{mb1.2}}$  and  $g_{\text{mb3.4}}$  are the bulk transconductance of transistors M1-M2 and M3-M4, respectively, and  $r_{o1}$  is the parallel of  $r_{d1.2}$ and  $r_{d3.4}$ . Care must be taken during the design phase, so that the denominator of (3) is always positive in all the process corners and temperature values. In conclusion, the gain increase is achieved by setting the denominator of (3) less than 1, but close to 1.

The overall OTA differential gain is given by

$$A_0 \approx G_{\text{mb}} g_{m6.8} g_{m12} \left( R_{A.B} / / r_{o1} \right) r_{o2} r_{o3} \tag{4}$$

where  $r_{o2}$  and  $r_{o3}$  are the output resistances of the second stage, equal to  $r_{d7}//r_{d8}$  and of the third stage (the main output), equal to  $r_{d10}//r_{d12}$ , respectively.

One of the main limitations of [10], of which this solution is an improved version, was the low CMRR, expressed by  $1/2 g_{m3} 4R_{A/R}$ , and that resulted in the range of a few decibels. In the proposed topology, CMRR is enhanced due to both the increased inputstage differential gain given by (3) and the differential to single ended conversion operated by current mirror M5-M7, not present in [10]. In fact, under perfect symmetry conditions (i.e., with the same common-mode currents generated by M6 and M8 and a unity current gain of M5-M7), the common-mode gain ideally nullifies. This condition requires that the drain voltages of M6 and M8 (and of course of M5 and M7) must be equal, yielding

$$V_{GS5} = V_{DD} - V_{SG12}. (5)$$

Such a condition nullifies systematic offset as well. Unfortunately, (5) is hardly met due to different pMOS and nMOS threshold voltage constraints and variations with process and temperature; therefore, a nonnegligible common-mode gain will still be present in an actual implementation.

Among the possible frequency compensation strategies, single Miller approach is exploited [24]. In particular, the frequency compensation is achieved through the Miller capacitor  $C_C$  connected between the output and the drain of M3. This is the first time that this type of compensation is successfully exploited in a body-driven OTA.

Denoting by  $c_{o2}$  the parasitic capacitance at the output of the second stage and by  $C_L$  the loading capacitance (not shown in Fig. 1), small-signal analysis reveals that the open-loop transfer function can be approximated as

$$A(s) = A_0 \frac{\left(1 + \frac{s}{z_1}\right) \left(1 + \frac{s}{z_2}\right) \left(1 - \frac{s}{z_3}\right)}{\left(1 + \frac{s}{p_1}\right) \left(1 + a_1 s + a_2 s^2\right) \left(1 + \frac{s}{p_4}\right)}$$

$$\approx A_0 \frac{\left(1 + \frac{s}{z_1}\right)}{\left(1 + \frac{s}{p_1}\right) \left(1 + a_1 s + a_2 s^2\right)}$$

(6)

where  $A_0$  is the same as in (4), and the other parameters are given in the following:

$$p_1 \approx \frac{1}{g_{m6,8}g_{m12} (R//r_{o1}) r_{o2}r_{o3}C_C + r_{o3}C_L}$$

(7)

$$a_1 \approx \frac{C_L \left( C_C R_{A,B} + 2c_{o2} r_{o2} \right)}{2} \tag{8}$$

$$a_2 \approx \frac{C_C C_L c_{o2} R_{A,B}^{-1} r_{o2}}{2} \tag{9}$$

$$z_1 \approx \frac{g_{m3,4}}{2C_C} \tag{10}$$

$$z_{1} \approx \frac{g_{m3,4}}{2C_{C}}$$

$$z_{2} \approx \frac{g_{m8}g_{m12}}{c_{o2} (g_{m10} - g_{m3,4})}$$

(10)

$$z_3 \approx \frac{g_{m10} - g_{m3,4}}{c_{Y2}} \tag{12}$$

$$z_{3} \approx \frac{g_{m10} - g_{m3,4}}{c_{X2}}$$

$$p_{4} \approx \frac{g_{m3,4}}{2c_{X2}}.$$

(12)

Note that the two last zeros and pole (all real) can be neglected because they depend on parasitic capacitances much lower than  $C_L$ and  $C_C$ , and hence, their values are at a frequency much higher than the GBW product, which, from (4) and (7), is expressed by

GBW =

$$A_0 p_1 = \frac{G_{\text{mb}}}{C_C + \frac{C_L}{g_{m6.8}g_{m12}(R//r_{o1})r_{o2}}}$$

. (14)

It should be observed that (14) reduces to the usual expression  $G_{\rm mb}/C_C$  for  $C_L \ll g_{m6,8}g_{m12}(R//r_{o2})r_{o2}$ . However, for  $C_L \gg$  $g_{m6,8}g_{m12}(R//r_{o2})r_{o2}$ , the GBW reduces with increasing values

TABLE I

TRANSISTOR ASPECT RATIOS AND CIRCUIT PARAMETERS

| Par.                | Value     | Par.               | Value                  | Par.        | Value     | Par.      | Value                  |

|---------------------|-----------|--------------------|------------------------|-------------|-----------|-----------|------------------------|

| $V_{DD}$            | 0.3 V     | $(W/L)_6, (W/L)_8$ | 9/0.18                 | $C_L$       | 50 pF     | $g_{m10}$ | 78.9 μS                |

| $I_B$               | 1.6 μA    | (W/L) <sub>9</sub> | 2.1/0.18               | $g_{m1,2}$  | 25.9 μS   | $g_{m12}$ | 74.7 μS                |

| $V_B$               | 150 mV    | $(W/L)_{10}$       | 12.6/0.18              | $g_{mb1,2}$ | 7.1 μS    | $r_{o1}$  | $304~\mathrm{k}\Omega$ |

| $(W/L)_1, (W/L)_2$  | 4.2/0.3   | $(W/L)_{11}$       | 9/0.18                 | $g_{mb3,4}$ | $3 \mu S$ | $r_{o2}$  | $845~k\Omega$          |

| (W/L) <sub>13</sub> | 4.2/0.3   | $(W/L)_{12}$       | 13.5/0.18              | $g_{m3,4}$  | 7.3 μS    | $r_{o3}$  | 110 kΩ                 |

| $(W/L)_3, (W/L)_4$  | 9/0.18    | $R_A, R_B$         | $200~\mathrm{k}\Omega$ | $g_{m7}$    | 14.8 μS   | $c_{o1}$  | 45 fF                  |

| $(W/L)_5, (W/L)_7$  | 0.45/0.18 | $C_C$              | 470 fF                 | $g_{m6,8}$  | 16.3 μS   | $C_{O2}$  | 62 fF                  |

Fig. 2. Simulated (a) ac response at different load capacitor values and (b) PM, GM, and GBW product versus load capacitor.

of  $C_L$ . Again, the positive feedback enhancing  $G_{\rm mb}$  is found beneficial also to improve GBW.

The evaluation of the phase margin (PM), yields

$$PM = \tan^{-1} \left( \frac{1 - a_2 \omega_{GBW}^2}{a_1 \omega_{GBW}} \right) + \tan^{-1} \left( \frac{\omega_{GBW}}{z_1} \right).$$

(15)

#### III. DESIGN AND SIMULATION RESULTS

The OTA in Fig. 1 was designed using a standard 65-nm CMOS technology provided by STMicroelectronics. The above equations were also considered during the design steps. Table I shows the main transistor aspect ratios and circuit parameters. The supply voltage,  $V_{\rm DD}$ , is 0.3 V ( $V_{\rm SS}=0$  V) and the total current consumption is 8.5  $\mu$ A. It is seen that  $g_{\rm mb3,4}R_{\rm A,B}//r_{o1}$  is about 0.36 providing a 1.56 boost in the transconductance, as anticipated by (3).

Assuming a load capacitance equal to 50 pF, the required value of  $C_C$  to get a PM of 70° is equal to only 470 fF.

Fig. 2(a) shows the simulated bode plot of the open-loop gain at various capacitive loads. As predicted by (14), GBW does not depend on  $C_L$  for  $C_L \ll g_{m6,8}g_{m12}(R//r_{o2})r_{o2} \approx 58$  pF. This result is confirmed by Fig. 2(b), where the PM, gain margin (GM), and GBW are simulated versus  $C_L$ . As a distinctive feature of the

TABLE II

CORNER ANALYSIS RESULTS

| T=-10°C               |       |       |       |       |       |  |  |  |  |

|-----------------------|-------|-------|-------|-------|-------|--|--|--|--|

| Parameter             | TT    | SS    | SF    | FS    | FF    |  |  |  |  |

| Power (µW)            | 2.3   | 1.9   | 2     | 2.2   | 2.7   |  |  |  |  |

| DC Gain (dB)          | 38.1  | 35.8  | 39    | 33.1  | 39.6  |  |  |  |  |

| GBW (MHz)             | 1.06  | 0.69  | 1.01  | 0.68  | 1.4   |  |  |  |  |

| Phase Margin (deg)    | 73.5  | 77.1  | 71.6  | 79.7  | 72.7  |  |  |  |  |

| Gain Margin (dB)      | -21.3 | -23.5 | -19.1 | -27.1 | -20.2 |  |  |  |  |

| Pos. Slew Rate (V/μs) | 0.44  | 0.27  | 0.98  | 0.22  | 0.86  |  |  |  |  |

| Neg. Slew Rate (V/us) | 0.28  | 0.18  | 0.26  | 0.24  | 0.45  |  |  |  |  |

| T=-27°C               |       |       |       |       |      |  |  |  |  |

|-----------------------|-------|-------|-------|-------|------|--|--|--|--|

| Parameter             | TT    | SS    | SF    | FS    | FF   |  |  |  |  |

| Power (µW)            | 2.8   | 2.4   | 2.5   | 2.8   | 3.3  |  |  |  |  |

| DC Gain (dB)          | 38.1  | 36.7  | 37.3  | 34.5  | 38.8 |  |  |  |  |

| GBW (MHz)             | 1.28  | 0.97  | 1.15  | 0.96  | 1.52 |  |  |  |  |

| Phase Margin (deg)    | 72.8  | 73.9  | 72.8  | 76.2  | 73.7 |  |  |  |  |

| Gain Margin (dB)      | -20.4 | -21.5 | -19.5 | -24.6 | -20  |  |  |  |  |

| Pos. Slew Rate (V/μs) | 0.61  | 0.41  | 0.98  | 0.34  | 0.86 |  |  |  |  |

| Neg. Slew Rate (V/μs) | 0.36  | 0.26  | 0.29  | 0.33  | 0.45 |  |  |  |  |

| T=-85°C               |       |      |       |       |       |  |  |  |  |

|-----------------------|-------|------|-------|-------|-------|--|--|--|--|

| Parameter             | TT    | SS   | SF    | FS    | FF    |  |  |  |  |

| Power (µW)            | 3.7   | 3.2  | 2.2   | 3.6   | 4.3   |  |  |  |  |

| DC Gain (dB)          | 35.3  | 35.3 | 30.9  | 34.1  | 35    |  |  |  |  |

| GBW (MHz)             | 1.32  | 1.16 | 0.99  | 1.19  | 1.41  |  |  |  |  |

| Phase Margin (deg)    | 75.7  | 74.3 | 79.3  | 75.7  | 77.9  |  |  |  |  |

| Gain Margin (dB)      | -21.1 | -21  | -23.2 | -23.1 | -21.5 |  |  |  |  |

| Pos. Slew Rate (V/μs) | 0.83  | 0.62 | 1.11  | 0.53  | 1.06  |  |  |  |  |

| Neg. Slew Rate (V/µs) | 0.4   | 0.34 | 0.29  | 0.42  | 0.44  |  |  |  |  |

TABLE III CORNER AND MONTE CARLO (1000 ITERATIONS) ANALYSIS RESULTS FOR  $T=27~^{\circ}\mathrm{C}$  (TT CORNER)

| Parameter                 | μ     | σ    |

|---------------------------|-------|------|

| Power (µW)                | 2.8   | 0.2  |

| DC Gain (dB)              | 38    | 0.5  |

| GBW (MHz)                 | 1.26  | 0.1  |

| Phase Margin (deg)        | 73    | 0.5  |

| Gain Margin(dB)           | -20.5 | 0.7  |

| Positive Slew Rate (V/µs) | 0.62  | 0.11 |

| Negative Slew Rate (V/µs) | 0.35  | 0.04 |

proposed solution, the OTA exhibits a PM higher than  $72^{\circ}$  for any capacity load. However, stability is reduced for low value of  $C_L$  due to reduced GM, which is caused by the reduction of the damping factor of complex and conjugate poles. Consequently, the amplifier is stable for capacitive loads greater than about 5 pF.

The simulation of the input-referred noise shows a value of the white noise equal to 250 nV/ $\sqrt{\text{Hz}}$  with a corner frequency value of about 10  $\mu$ V/ $\sqrt{\text{Hz}}$ .

The robustness of the OTA against process and temperature variations has been assessed through extensive corner analysis. The results are summarized in Tables II for the various transistor corners and at  $-10~^{\circ}\text{C}$ , 27  $^{\circ}\text{C}$ , and 85  $^{\circ}\text{C}$ , assuming  $C_L = 50~\text{pF}$ . The amplifier is apparently stable in all cases.

Additional analyses were executed considering a  $\pm 10\%$  variation of the power supply, confirming the robustness of the OTA.

Finally, 1000 Monte Carlo simulations have been executed, and the results are summarized in Table III, showing a relative standard deviation lower than 20% in all cases.

## IV. EXPERIMENTAL RESULTS

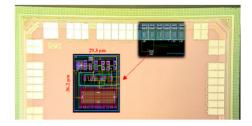

Fig. 3 depicts the layout of the OTA superimposed to the chip microphotograph. The occupied area is  $10.6 \cdot 10^{-3}~\text{mm}^2$ .

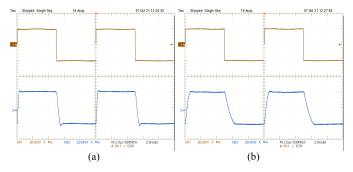

Fig. 4(a) and (b) shows the measured open-loop frequency response for  $C_L = 50$  pF and  $C_L = 150$  pF, respectively, of one of the fabricated prototypes. The dc gain is around 40 dB and GBW is

TABLE IV

SUMMARY OF MEASURED PERFORMANCE METRICS AND COMPARISON

WITH OTHER MULTISTAGE EXPERIMENTALLY TESTED SUB-1-V OTAS

|                                                                     |       |      |      | ,      | ,      | ,      | ,          |        |

|---------------------------------------------------------------------|-------|------|------|--------|--------|--------|------------|--------|

| Ref.                                                                | [4]   | [10] | [21] | [11]   | [12]   | [13]   | This work* |        |

| Year                                                                | 2016  | 2016 | 2017 | 2018   | 2020   | 2020   | 20         | 22     |

| Tech. (nm)                                                          | 180   | 180  | 350  | 180    | 180    | 65     | 6          | 5      |

| Op. mode**                                                          | GD    | BD   | GD   | BD     | BD     | BD     | BD         |        |

| # stages                                                            | 2     | 3    | 2    | 2      | 3      | 3      | 3          |        |

| Area (mm <sup>2</sup> ×10 <sup>-3</sup> )                           | 36    | 19.8 | 14.0 | 8.2    | 9.8    | 2.0    | 1.06       |        |

| Supply voltage(V)                                                   | 0.5   | 0.7  | 0.7  | 0.3    | 0.3    | 0.25   | 0.3        |        |

| $C_L$ (pF)                                                          | 40    | 20   | 10   | 20     | 30     | 15     | 50         | 150    |

| DC gain (dB)                                                        | 77    | 57   | 65   | 63     | 98.1   | 70     | 38         |        |

| I <sub>BIAS</sub> (µA)                                              | 0.14  | 36   | 27   | 0.056  | 0.043  | 0.104  | 8.5        |        |

| GBW (MHz)                                                           | 0.004 | 3    | 1    | 0.0028 | 0.0031 | 0.0095 | 1.65       | 0.81   |

| <i>PM</i> (°)                                                       | 56    | 60   | 60   | 61     | 54     | 88     | 70.3       | 71.3   |

| SR (V/µs)                                                           | 0.002 | 2.8  | 0.25 | 0.0071 | 0.0091 | 0.002  | 0.18       | 0.12   |

| CMRR (dB)                                                           | 55    | 19   | 45   | 72     | 60     | 62.5   | 39.8       |        |

| PSRR (dB)                                                           | 52    | 52   | 50   | 62     | 61     | 38     | 44.7       |        |

| IFOM <sub>S</sub><br>(MHz·pF/μA) <sup>(1)</sup>                     | 1.14  | 1.67 | 0.37 | 1.00   | 2.15   | 1.37   | 9.71       | 14.29  |

| <i>IFOM</i> <sub>L</sub><br>(V/μs·pF/μA) <sup>(2)</sup>             | 0.57  | 1.56 | 0.09 | 2.54   | 6.30   | 0.29   | 1.06       | 2.12   |

| IFOM <sub>AS</sub><br>(MHz·pF/μA·mm <sup>2</sup> ) (3)              | 31.8  | 84.2 | 26.5 | 122    | 219    | 685    | 9156.5     | 13485  |

| IFOM <sub>AL</sub><br>(V/μs·pF/μA· mm <sup>2</sup> ) <sup>(4)</sup> | 15.9  | 78.6 | 6.61 | 309.2  | 642.9  | 144.2  | 998.9      | 1997.8 |

<sup>\*</sup>Average values over six samples.

$${^{(1)}}IFOM_S = \frac{GBW}{I_{bias}}C_L^{~(2)}IFOM_L = \frac{SR}{I_{bias}}C_L^{~(3)}IFOM_S = \frac{GBW}{I_{bias} \cdot Area}C_L^{~(4)}IFOM_L = \frac{SR}{I_{bias} \cdot Area}C_L^{~(4)}IFOM_L = \frac{SR}{I_{bias} \cdot Area}C_L^{~(5)}IFOM_L = \frac{SR}{I_{bias}}C_L^{~(5)}IFOM_L = \frac{SR}{I_{bias}}C_L^{~(5)}IFOM_L$$

Fig. 3. OTA layout and chip microphotograph.

1.65 MHz for  $C_L=50$  pF and 0.77 MHz for  $C_L=150$  pF and with a PM of nearly 66° for  $C_L=50$  pF and 70° for  $C_L=150$  pF.

The measured response of the same prototype to a 40-mV<sub>pp</sub> step is illustrated in Fig. 5(a) and (b) for  $C_L=50$  pF and  $C_L=150$  pF, respectively. Positive/negative SR and 1%-settling time are, respectively, equal to 0.25/-0.11 V/ $\mu$ s and 0.31/0.7  $\mu$ s for  $C_L=50$  pF. The same parameters for  $C_L=150$  pF are equal to 0.17/-0.07 V/ $\mu$ s and 0.62/1.26  $\mu$ s. The maximum input current when a 300-mV<sub>pp</sub> step is applied is equal to about 600 nA.

The experimental characterization of the OTA for lower capacitive loads was not possible due to the loading effect of the package, test PCB, and probes, which accounts for a parasitic load almost equal to 50 pF.

Six different samples have been experimentally characterized, and the mean values of the main amplifier performance metrics are summarized in the last column of Table IV, which compares the proposed solution with other recent multistage sub-1-V OTAs. The proposed solution has the lowest area consumption, operates under one of the lowest supply voltages, and can drive the largest load capacitor with one of the best GBW achieved.

The traditional figures of merit, whose expressions are reported at the bottom of Table IV, are adopted to compare the different amplifiers. It can be noted that other solutions exhibit a higher value of IFOM<sub>L</sub> than the proposed OTA (namely, [10], [11], [12] for  $C_L = 50$  pF and [11], [12] for  $C_L = 150$  pF), whereas IFOM<sub>S</sub> is higher

Fig. 4. Measured bode diagram of the OTA loop gain with (a)  $C_L=50~{\rm pF}$  and (b)  $C_L=150~{\rm pF}$ .

Fig. 5. Measured step response in unity gain configuration with (a)  $C_L=50~{\rm pF}$  and (b)  $C_L=150~{\rm pF}$ .

than the other solutions by  $4.5 \times$  and  $6.6 \times$  for  $C_L$  equal to 50 and 150 pF, respectively.

Moreover, when IFOM<sub>AS</sub> and IFOM<sub>AL</sub> are considered, the proposed OTA exhibits an improvement equal to about  $13 \times$  and  $1.5 \times$  for  $C_L = 50$  pF and  $20 \times$  and  $3 \times$  for  $C_L = 150$  pF, when compared to the other solutions. As a main drawback, the lowest dc gain is displayed by the proposed OTA.

# V. CONCLUSION

A bulk-driven three-stage OTA exploiting positive feedback and a single Miller capacitor has been proposed and experimentally validated. The solution can work under a 0.3-V supply and exhibits class AB operation, amenable to drive a 50-pF load with an SR of 0.18 V/ $\mu$ s and a GBW of 1.65 MHz. The proposed OTA is a good candidate for area-constrained ultralow-voltage, ultralow-power applications, such as wireless sensor nodes and implantable biomedical devices. The adoption (apart from M1–M2 and M13) of transistors of the digital core of the design kit has led to a dc

<sup>\*\*</sup>GD: gate-driven; BD: bulk-driven

gain equal to 38 dB, due to the reduced intrinsic output resistance offered by these devices. However, additional circuit techniques relying on local positive feedback can be adopted to increase the gain as those proposed in [14], [15], and [16]. Moreover, the lack of a tail current generator for the first stage leads to reduced values of power supply rejection ratio (PSRR) and CMRR, which, nevertheless, still offer acceptable values. The proposed OTA can be exploited in all the applications requiring sub-0.5-V supply and rail-to-rail input operation, like IoT nodes directly powered by single silicon solar cells.

#### REFERENCES

- [1] M. Alioto, Ed., Enabling the Internet of Things: From Integrated Circuits to Integrated Systems. Cham, Switzerland: Springer, 2017.

- [2] T. Stockstad et al., "A 0.9-V 0.5-μm rail-to-rail CMOS operational amplifier," *IEEE J. Solid-State Circuits*, vol. 37, no. 3, pp. 286–292, Mar. 2002.

- [3] A. D. Grasso, D. Marano, G. Palumbo, and S. Pennisi, "Design methodology of subthreshold three-stage CMOS OTAs suitable for ultra-low-power low-area and high driving capability," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 6, pp. 1453–1462, Jun. 2015.

- [4] Z. Qin, A. Tanaka, N. Takaya, and H. Yoshizawa, "0.5-V 70-nW rail-to-rail operational amplifier using a cross-coupled output stage," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 63, no. 11, pp. 1009–1013, Nov. 2016.

- [5] A. D. Grasso and S. Pennisi, "Ultra-low power amplifiers for IoT nodes," in *Proc. 25th IEEE Int. Conf. Electron., Circuits Syst. (ICECS)*, Dec. 2018, pp. 497–500.

- [6] B. J. Blalock, P. E. Allen, and G. A. Rincon-Mora, "Designing 1-V op amps using standard digital CMOS technology," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 45, no. 7, pp. 769–780, Jul. 1998.

- [7] P. Monsurro, S. Pennisi, G. Scotti, and A. Trifiletti, "Exploiting the body of MOS devices for high performance analog design," *IEEE Circuits Syst. Mag.*, vol. 11, no. 4, pp. 8–23, 4th Quart., 2011.

- [8] L. H. C. Ferreira and S. R. Sonkusale, "A 60-dB gain OTA operating at 0.25-V power supply in 130-nm digital CMOS process," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 6, pp. 1609–1617, Jun. 2014.

- [9] O. Abdelfattah, G. W. Roberts, I. Shih, and Y.-C. Shih, "An ultra-low-voltage CMOS process-insensitive self-biased OTA with rail-to-rail input range," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 10, pp. 2380–2390, Oct. 2015.

- [10] E. Cabrera-Bernal, S. Pennisi, A. D. Grasso, A. Torralba, and R. G. Carvajal, "0.7-V three-stage class-AB CMOS operational transconductance amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 11, pp. 1807–1815, Nov. 2016.

- [11] T. Kulej and F. Khateb, "Design and implementation of sub 0.5-V OTAs in 0.18-μm CMOS," *Int. J. Circuit Theory Appl.*, vol. 46, no. 6, pp. 1129–1143, Jun. 2018.

- [12] T. Kulej and F. Khateb, "A 0.3-V 98-dB rail-to-rail OTA in 0.18  $\mu$ m CMOS," *IEEE Access*, vol. 8, pp. 27459–27467, 2020.

- [13] K.-C. Woo and B.-D. Yang, "A 0.25-V rail-to-rail three-stage OTA with an enhanced DC gain," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 7, pp. 1179–1183, Jul. 2020.

- [14] F. Khateb and T. Kulej, "Design and implementation of a 0.3-V differential difference amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 2, pp. 513–523, Feb. 2019.

- [15] A. Ballo, A. D. Grasso, and S. Pennisi, "0.4-V, 81.3-nA bulk-driven single-stage CMOS OTA with enhanced transconductance," *Electronics*, vol. 11, no. 17, p. 2704, Aug. 2022.

- [16] F. Khateb, M. Kumngern, T. Kulej, and D. Biolek, "0.5 V differential difference transconductance amplifier and its application in voltage-mode universal filter," *IEEE Access*, vol. 10, pp. 43209–43220, 2022.

- [17] F. Centurelli, R. D. Sala, P. Monsurró, P. Tommasino, and A. Trifiletti, "An ultra-low-voltage class-AB OTA exploiting local CMFB and body-to-gate interface," AEU Int. J. Electron. Commun., vol. 145, Feb. 2022, Art. no. 154081.

- [18] M. Akbari, S. M. Hussein, Y. Hashim, and K.-T. Tang, "0.4-V tail-less quasi-two-stage OTA using a novel self-biasing transconductance cell," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 69, no. 7, pp. 2805–2818, Jul 2022

- [19] T. Kulej, F. Khateb, D. Arbet, and V. Stopjakova, "A 0.3-V high linear rail-to-rail bulk-driven OTA in 0.13 μm CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 4, pp. 2046–2050, Apr. 2022.

- [20] H. F. Baghtash, "A 0.4 V, body-driven, fully differential, tail-less OTA based on current push-pull," *Microelectron. J.*, vol. 99, May 2020, Art. no. 104768.

- [21] A. D. Grasso, S. Pennisi, G. Scotti, and A. Trifiletti, "0.9-V class-AB Miller OTA in 0.35-μm CMOS with threshold-lowered non-tailed differential pair," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 7, pp. 1740–1747, Jul. 2017.

- [22] A. Ballo, A. D. Grasso, S. Pennisi, and G. Susinni, "300-mV bulk-driven three-stage OTA in 65-nm CMOS," in *Proc. SIE* (Lecture Notes in Electrical Engineering). Cham, Switzerland: Springer, 2023, p. 1520, doi: 10.1007/978-3-031-26066-7

- [23] A. Ballo, A. D. Grasso, and S. Pennisi, "Active load with cross-coupled bulk for high-gain high-CMRR nanometer CMOS differential stages," *Int. J. Circuit Theory Appl.*, vol. 47, no. 10, pp. 1700–1704, Oct. 2019.

- [24] A. D. Grasso, D. Marano, G. Palumbo, and S. Pennisi, "Single Miller capacitor frequency compensation techniques: Theoretical comparison and critical review," *Int. J. Circuit Theory Appl.*, vol. 50, no. 5, pp. 1462–1486, May 2022.