# Hybrid Cascode Frequency Compensation for Four-Stage OTAs Driving a Wide Range of $C_L$

Hamed Aminzadeh<sup>©</sup>, *Member, IEEE*, Andrea Ballo<sup>®</sup>, *Member, IEEE*, Alfio Dario Grasso<sup>®</sup>, *Senior Member, IEEE*, Mohammad M. Valinezhad<sup>®</sup>, *Member, IEEE*, and Mohammad Jamali

Abstract-Feedback amplifiers consisting of multiple gain stages are used to establish highly accurate buffered/amplified signals that can drive a wide range of capacitive load (CL). This article models, analyzes, and presents the measurement results of a high-gain four-stage operational transconductance amplifier (OTA) that is able to handle a wide range of CL up to infinity. In addition to local compensation capacitors and nulling resistors in the intermediate stages, two high-speed feedback loops made by parallel Miller capacitors and current buffers provide Miller compensation and the consequent pole-splitting in the lower CL range. The dominant pole is made dependent on the CL for the higher CL range, enabling the maintenance of the stability conditions up to infinite CL. The proposed amplifier was integrated into a 65-nm CMOS technology, consuming 140-µA static current under a 1.2-V supply and an active area of 0.0086 mm<sup>2</sup>. A dc gain greater than 100 dB was also perceived with a unity-gain frequency (UGF) of 4.09, 2.01, and 0.27 MHz for 4.7, 10, and 100-nF load capacitors, respectively. The average slew rate (SR) is 0.59 V/ $\mu$ s, when the OTA is formed as a buffer targeting the CLs higher than 4.7-nF.

Index Terms—Capacitive load (CL), frequency compensation, miller effect, multistage, operational transconductance amplifiers (OTA), slew-rate (SR), stability, unity-gain frequency (UGF).

## I. INTRODUCTION

THE continuous trend toward the scaling of MOS transistors has been followed by reducing the voltage supply  $(V_{\rm DD})$  to guarantee a safe operation under very low power constraints. Meanwhile, short-channel MOS devices suffer from reduced intrinsic gain [1], and traditional gain-boosting solutions like cascading have been progressively abandoned in low-voltage nano-scale bulk CMOS technologies [2]. Although FinFET technologies (i.e., technology nodes lower than 16 nm) exhibit sufficient intrinsic gain, the majority of commercial analog products are still fabricated with conventional higher than 32 nm bulk technologies. Enlarging the gain of the amplifiers in scaled bulk CMOS (down to 32 nm) can be therefore accomplished by resorting to

Manuscript received 25 May 2023; revised 16 August 2023; accepted 6 September 2023. (Corresponding author: Alfio Dario Grasso.)

Hamed Aminzadeh, Mohammad M. Valinezhad, and Mohammad Jamali are with the Department of Electrical Engineering, Payame Noor University (PNU), Tehran 4697-19395, Iran (e-mail: aminzadeh@pnu.ac.ir; mm.valinezhad@ieee.org).

Andrea Ballo and Alfio Dario Grasso are with Dipartimento di Ingegneria Elettrica Elettronica e Informatica (DIEEI), University of Catania, 95124 Catania, Italy (e-mail: andrea.ballo@unict.it; agrasso@dieei.unict.it).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TVLSI.2023.3313613.

Digital Object Identifier 10.1109/TVLSI.2023.3313613

the multiple gain stages cascaded. Efficient implementation of multistage amplifiers has not been, however, straightforward and thus the focus of extensive research over the last decades [3], [4], [5]. Within this framework, one of the commonly used applications of the high-gain operational transconductance amplifiers (OTAs) was to provide a reliable amplified signal for the capacitive loads (CLs) reaching tens of nanofarad. Some principal blocks that call for such specifications are active-matrix liquid crystal displays (LCDs), low-dropout regulators (LDOs), active filters, analog-to-digital converters, and line drivers [6], [7], [8], [9], [10], [11].

Maintaining the loop stability is the main challenge of the feedback OTAs supporting a wide  $C_L$  range [2], [5], [12]. Each stage adds a high-impendence node and, consequently, a dominant pole in the transfer function which potentially depends on the loading conditions, so keeping the OTA stable over a broad  $C_L$  range entails a carefully designed compensation network. The size of the CL is highly variable in some applications, preventing the optimization of the transistor sizes irrespective of  $C_L$ . In the case of a headphone driver, e.g., the external load is dependent on the type of cable connected to the output and its size may vary between a few picofarads to several nanofarads [13]. The  $C_L$  variations may not be aggressive in those designs used for LCD drivers, but a general-purpose amplifier is highly desirable to prevent multiple design cycles by supporting a wide range of static CLs. Single- or two-stage feedback OTAs handling a wide  $C_L$  range can be conveniently designed and stabilized using the commonly used architectures [14], [15], [16], [17]. Indeed, at least three stages are needed to overcome the gain requirement of several customary applications in recent technologies. It soon became apparent that two compensation capacitors, both of which are dependent on  $C_L$ , are required to stabilize a three-stage amplifier using classical nested Miller compensation (NMC) [4], [18]. [19], [20], [21]. As such, the bandwidth is severely limited and ends up with inferior power and area efficiencies due to improper placement of poles/zeros setting aside the loading conditions of the amplifier. Sophisticated design strategies for three-stage amplifiers thus tend to eliminate the second capacitor and enrich the so-called single-Miller capacitor (SMC) compensation method with auxiliary current buffers, local RC networks, and feedforward stages, so additional left-half-plane (LHP) zeros are generated and nondominant poles can be moved to higher frequencies for the minimum area and power consumption [22], [23], [24], [25].

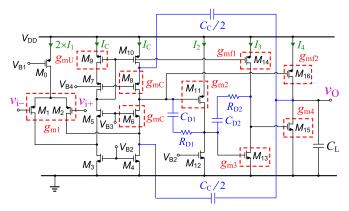

Fig. 1. Schematic of the proposed OTA.

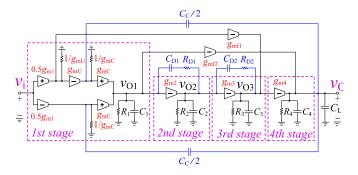

Fig. 2. Block diagram of the OTA in Fig. 1.

Capacitor-free compensation strategies have been also reported at the cost of inferior power efficiency relative to the capacitor-based solutions [26], [27]. Among the possible ways to realize a stable three-stage OTA, hybrid-cascode frequency compensation [28], [29] was originally developed from the idea of Miller compensation employing current buffers [23], [24], and proved to be very efficient especially when combined to the local RC network for achieving a wide  $C_L$  drivability range [2]. According to the original strategy, the Miller capacitor is split into equal fractions, and each fraction is applied to build up a unilateral feedback pathway to the first stage through a current buffer. The original compensation loop is thus divided into parallel loops to detect the output signal with a higher feedback factor, thus boosting the overall efficiencies in terms of area and power. The additional feedback is carefully incorporated into the circuit topology without sacrificing area or power and by exploiting the original resources of the amplifier only [2]. In the case of threestage OTAs, experimental results thus reflected substantial improvements from the CL range, size of  $C_C$ , silicon footprint, and power aspects [2]. As intrinsic gain and channel length of transistors continue to scale down, four-stage amplification is becoming more essential to maintain both dynamic range and the gain requirements in nano-scale technologies. By contrast, the frequency compensation of four-stage amplifiers appears to be much more complicated especially when a wide  $C_L$  range is demanded [30], [31], [32], [33].

In this work, we extend the idea of hybrid-cascode frequency compensation to four-stage OTAs by combining it with local compensation capacitors and resistors so that acceptable

stability margins can be maintained over a wide  $C_L$  range (from 4.7-nF to infinity, as confirmed by the experimental results). The remainder of this contribution is structured as follows. Section II analyzes the topology, block diagram, and small- and large-signal conditions of the new amplifier. Section III is devoted to the design procedures and the prerequisite stability analysis. In Section IV, we show the simulation and experimental results and compare the performance metrics with the relevant art. Finally, Section V concludes the article.

#### II. PROPOSED TOPOLOGY

#### A. Circuit Schematic

Fig. 1 presents a possible implementation of the proposed four-stage OTA, where  $v_i = v_{i+} - v_{i-}$  is the input voltage and  $v_O$  is the output. The input stage  $g_{m1}$  is made by  $M_0-M_{10}$  with  $M_0$  to power up the input devices. The current mirror devices  $M_9$ – $M_{10}$  perform the differential to single-ended conversion. The complementary MOS devices  $M_{11}$ – $M_{12}$ ,  $M_{13}$ – $M_{14}$ , and  $M_{15}$ - $M_{16}$  constitute the second, third, and fourth inverting stages between the supply rails where  $g_{m2}$ ,  $g_{m3}$ , and  $g_{m4}$ are their equivalent transconductances, respectively. Transistors  $M_{14}$  and  $M_{16}$  implement the feedforward stages with transconductances  $g_{mf1}$  and  $g_{mf2}$ , which assist in improving the large-signal operation by forming class-AB third and fourth stages topologies. The quiescent current of the output branch is decided by the second stage current since  $M_{11}$ and  $M_{16}$  share the same source-gate voltage. To establish a more stable quiescent current for the output stage, either  $M_{15}$  or  $M_{16}$  can be biased via a low impedance node in the form of a class-A configuration. Such approach is not, however, effective in terms of dynamic load drivability and static power consumption. The biasing voltages  $V_{B1}$ – $V_{B4}$  are accompanied by a biasing circuitry not illustrated for the sake of conciseness. It is worth noting that the circuit topology is very simple and entails the same number of transistors of a three stage OTA since the second, third, and fourth stages are all inverting.

The main elements of the frequency compensation network are the series  $R_{D1}$ ,  $C_{D1}$ , and  $R_{D2}$ ,  $C_{D2}$  around the second and the third stages, respectively, besides the Miller  $C_C/2$  capacitors between  $v_O$  and the source of  $M_6$  and  $M_8$  that implement the embedded  $g_{mC}$  transconductances without any power overhead. These devices with a relatively light  $1/g_{mC}$  input impedance close the parallel feedback pathways from  $v_O$  to the input, moving a right-half-plane (RHP) zero to very high frequencies by minimizing a feedforward current to flow to the output via either  $C_C/2$  [34]. The hybrid nature of the compensation network also allows designers to achieve a balanced time response during the falls and rises of  $v_O$ , unlike the classical solution which possibly connects  $C_C$  to the source of  $M_6$  or  $M_8$ .

## B. Small-Signal Analysis

Fig. 2 depicts the amplifier diagram of the proposed fourstage OTA, where identical symbols as in Fig. 1 are utilized to represent similar elements. It contains a front-end differential stage followed by inverting second, third, and fourth stages, all of which are modeled by a transconductance  $g_{mi}$ , output resistor  $R_i$ , and output capacitor  $C_i$  (i = 1, 2, 3, 4). The feedforward stages  $g_{mf1}$  and  $g_{mf2}$  have negligible effect on the small-signal operation, but are intended for improving the large-signal operation [2], [24]. The compensation network contains  $C_C$  broken into equal fractions, and each fraction forms a feedback loop consistent with the earlier descriptions. It will be shown later that the new arrangement pushes to a higher frequency the magnitude of the nondominant poles and lowers their quality factor, Q, when compared to a single feedback loop potentially closed by  $C_C$ . One-way  $g_{mC}$  current buffers are placed in series with the Miller capacitors to represent the contribution of  $M_6$  or  $M_8$  in Fig. 1. The small input impedance of the current buffers extends the bandwidth of the compensation loop by relaxing the  $C_C$  loading on  $v_O$ . As for the series  $C_{D1}$ ,  $R_{D1}$  and  $C_{D2}$ ,  $R_{D2}$ , they enhance the stability of the inner gain-stages while contributing to the overall stability not by introducing a low-frequency zero only but also by reducing the Q-factor of the poles as will be analyzed later.

A voltage-gain transfer function based on the amplifier diagram in Fig. 2 is a prerequisite to exploring the different aspects of the proposed OTA in the presence of  $C_L$  variations. The exact transfer function is excessively complex, containing several terms related to the stages' output impedances, their equivalent transconductors, and compensation elements. Many terms can be simplified upon  $R_i \gg R_{D1}$ ,  $R_{D2} \gg 1$ ,  $g_{mi}R_i \gg$ 1, and  $C_L \gg C_C$ ,  $C_{D1}$ ,  $C_{D2} \gg C_i$  for i, j = 1, 2, 3, 4, for the output impedances are subsequently dominated by  $C_L$ ,  $g_{mi}$ and compensation elements. Under these circumstances, the methodology described in [34] can be used to approximate  $v_O/v_i$  as

$$A_{V}(s) = \frac{v_{O}}{v_{i}} \approx \frac{A_{0} \left(1 + \frac{s}{z_{1}}\right) \left(1 + \frac{s}{z_{2}}\right)}{\left(1 + \frac{s}{P - 3dB}\right) \left(1 + \frac{s}{Q\omega_{0}} + \frac{s^{2}}{\omega_{0}^{2}}\right)}$$

(1)

where

$$A_0 \approx g_{m1} g_{m2} g_{m3} g_{m4} R_1 R_2 R_3 R_4 \tag{2}$$

and

$$p_{-3dB} = -\frac{1}{g_{m2}g_{m3}g_{m4}R_1R_2R_3R_4C_C + R_4C_L}$$

(3)

denote the dc gain and the main pole, respectively. The transfer function contains two nondominant poles, whose Q-factor and natural frequency  $\omega_0$  are given as

$$\omega_{0} = \sqrt{\frac{2g_{mC}g_{m2}g_{m3}g_{m4}(R_{D1}C_{D1} + R_{D2}C_{D2})}{(g_{m2} + g_{m3})C_{D1}C_{D2}C_{L}}}}$$

$$Q = \frac{1}{R_{D1}R_{D2} + \frac{g_{m2} + g_{m3}}{g_{m2}g_{m3}g_{m4}} \left(1 + \frac{C_{L}}{C_{C}}\right)}$$

$$\times \sqrt{\frac{(g_{m2} + g_{m3})(R_{D1}C_{D1} + R_{D2}C_{D2})C_{L}}{2g_{mC}g_{m2}g_{m3}g_{m4}C_{D1}C_{D2}}}$$

$$\approx C_{C}\sqrt{\frac{g_{m2}g_{m3}g_{m4}(R_{D1}C_{D1} + R_{D2}C_{D2})}{2g_{mC}(g_{m2} + g_{m3})C_{D1}C_{D2}C_{L}}}.$$

(5)

These latter equations show that as follows.

- 1) Increasing  $C_L$  lowers the Q factor, thus leading up to two real poles when the OTA should drive an ultralarge load capacitor.

- 2) The coefficient "2" appearing in the Q factor and  $\omega_0$ expressions stems from the parallel loops implemented by dual  $C_C/2$ . Not only  $\omega_0$  is pushed to higher frequencies by this coefficient, but the Q factor is also reduced, both of which are in favor of stability.

- 3) The Q factor is governed by  $R_{D1}$  and  $R_{D2}$  rather than the output resistors  $R_2$  and  $R_3$ . This means that reducing the compensating resistors assist in improving the gain margin (GM) by dropping the Q factor without sacrificing the dc gain. Too low  $R_{D1}$  or  $R_{D2}$  are accompanied by compromised stability as they excessively lower  $\omega_0$ and, in turn, the phase margin (PM) of the exterior loop. Therefore, these resistors should be tuned to optimally position the nondominant poles relative to the time and frequency requirements of the application.

The derived transfer function also involves the LHP  $z_1$ and the RHPz2 located at high frequencies, in which their magnitude is

$$z_{1} = \frac{R_{D1}C_{D1} + R_{D2}C_{D2}}{R_{D1}R_{D2}C_{D1}C_{D2}} = \frac{1}{R_{D1}C_{D1}} + \frac{1}{R_{D2}C_{D2}}$$

(6)

$$z_{2} = -\frac{2g_{mC}g_{m2}g_{m3}g_{m4}R_{D1}R_{D2}}{(g_{m2} + g_{m3})C_{C}}.$$

(7)

$$z_2 = -\frac{2g_{mC}g_{m2}g_{m3}g_{m4}R_{D1}R_{D2}}{(g_{m2} + g_{m3})C_C}. (7)$$

The LHP zero depends on all  $C_{D1}$ ,  $C_{D2}$ , and  $R_{D1}$  and  $R_{D2}$ , and should be positioned to nullify partially the negative phase shift caused by the nondominant poles. As for the RHP zero, it is proportional to the compensating resistors, Miller capacitor and the  $g_m$  factors, and should be located well after the gain-bandwidth (GBW) product for its contribution not to reduce the stability margins. From (2) and (3) the GBW is expressed by

GBW =

$$A_0 \cdot |p_{-3\text{dB}}| = \frac{g_{m1}}{C_C + C_L / g_{m2} g_{m3} g_{m4} R_1 R_2 R_3}$$

. (8)

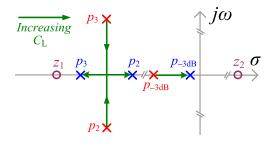

As for  $C_L \ll g_{m2}g_{m3}g_{m4}R_1R_2R_3C_C$ , the above expression is simplified to the maximum  $g_{m1}/C_C$ , reducing gradually to  $g_{m1}g_{m2}g_{m3}g_{m4}R_1R_2R_3/C_L$  under the heavy capacitive loading conditions. Depending on the size of  $C_C$ , the classical  $g_{m1}/C_C$ relation thus holds only in the lower range of  $C_L$  (say up to a few nanofarad). This means that the role of  $C_C$  is substituted by  $C_L$  when the amplifier should handle a very large load capacitors load. Endorsed by measurement results, scaling of the GBW via  $C_L$  can be exploited to optimize the stability conditions and to widen the upper  $C_L$  limit up to infinity. The movement of the poles/zeros is sketched in Fig. 3 by enlarging  $C_L$ , indicating that increasing the CL converts to real poles the original complex and conjugate poles and pushes the first pole toward the origin.

The transconductances of  $M_6$  and  $M_8$  were assumed to be identical in the foregoing analysis. While perfect matching can never be met using different types of  $M_6$  and  $M_8$  in Fig. 1, we anticipate that small mismatches between their  $g_{mC}$ trivially alter the positioning of the poles and zeros [2].

Fig. 3. Pole-zero map of the proposed OTA against  $C_L$ .

## C. Large-Signal Analysis

The large-signal step response is generally described by slew rate (SR) instead of the small-signal GBW, GM, and PM parameters. Referred to as the maximum rate of deviation, the SR is defined by the available current that can charge or discharge the parasitic and load capacitors connected to the gain stage outputs. By denoting  $I_{A1} \approx I_C$ ,  $I_{A2} \approx I_2$ ,  $I_{A3} \approx I_3$ , and  $I_{A4} \approx I_4$  as the upper limit of the currents that can be fed to the loading of the first stage  $C_{L1} \approx C_{D1} + C_C/2 + C_C/2 = C_{D1} + C_C$ , second stage  $C_{L2} \approx C_{D1} + C_{D2}$ , third stage  $C_{L3} \approx C_{D2}$ , and the final stage  $C_{L4} \approx C_C + C_L$  in Fig. 1, further by assuming that the parasitics are negligible when compared to the load and compensation capacitors, the SR will be the minimum among the following contributors:

$$SR \approx \min(SR_1, SR_2, SR_3, SR_4)$$

$$= \min\left(\frac{I_{A1}}{C_{L1}}, \frac{I_{A2}}{C_{L2}}, \frac{I_{A3}}{C_{L3}}, \frac{I_{A4}}{C_{L4}}\right). \tag{9}$$

The above relation is nominally restricted by  $SR_1$  and  $SR_4$  for small and heavy CLs, respectively. As for  $M_{16}$  in Fig. 1, it manages to improve the SR by forming an output push–pull stage capable of boosting the output current  $I_{A4}$  under the undesired output transitions. The use of SR boosters can help drive ultralarge CLs more effectively [30].

The above SR analysis models the average trend of the realistic *SR* only. Completely symmetrical positive/negative SR (SR+/SR-) never happens in practice, as different type of devices with potentially unequal gate inputs switch on/off and affect the charging/discharging rates of the capacitive loading in different stages.

#### III. STABILITY ANALYSIS AND DESIGN PROCEDURES

#### A. Analysis of Stability

Let us apply the key expressions derived in Section II to characterize PM and GM in terms of  $C_L$ . Using the GM definition as the starting point, it can be derived from (1) as

$$GM = -20\log\left(\frac{\sqrt{\left[1 + \left(\frac{PX}{z_1}\right)^2\right]\left[1 + \left(\frac{PX}{z_2}\right)^2\right]}}{\frac{PX}{GBW}\sqrt{\left(1 - \frac{PX^2}{\omega_0^2}\right)^2 + \left(\frac{PX}{Q\omega_0}\right)^2}}\right)$$

(10)

where PX is the phase crossover frequency derived as follows:

$$\tan^{-1} \left[ \frac{PX}{\omega_0 Q \left( 1 - PX^2 / \omega_0^2 \right)} \right] - \tan^{-1} \left( \frac{PX}{z_1} \right)$$

$$+ \tan^{-1} \left( \frac{PX}{z_2} \right) = 90^{\circ}. \quad (11)$$

A solution for the above relationship is

$$PX = \omega_0 \sqrt{\frac{\left(\frac{1}{R_{D1}C_{D1}} + \frac{1}{R_{D2}C_{D2}}\right)C_C}{\left(\frac{1}{R_{D1}C_{D1}} + \frac{1}{R_{D2}C_{D2}}\right)C_C - 2g_{mC}}}.$$

(12)

For the usual  $R_{D1}$ ,  $R_{D2}$ , and  $g_{mC}$ , provided that

$$\left(\frac{1}{R_{D1}C_{D1}} + \frac{1}{R_{D2}C_{D2}}\right)C_C \gg 2g_{mC}$$

(13)

the former will be reduced to  $PX \approx \omega_0$ , so the GM can be written as

$$\begin{array}{l}

\text{GM} \\

\approx 20 \log \left( \frac{\omega_0}{\text{GBWQ}} \right) - 10 \log \left[ 1 + \left( \frac{\omega_0}{z_1} \right)^2 \right] \\

- 10 \log \left[ 1 + \left( \frac{\omega_0}{z_2} \right)^2 \right] = \\

\approx 20 \log \left[ \frac{2g_{mC}}{g_{m1}} \left( 1 + \frac{C_L}{g_{m2} g_{m3} g_{m4} R_1 R_2 R_3 C_C} \right) \right] \\

- 10 \log \left[ 1 + \frac{2g_{mC} g_{m2} g_{m3} g_{m4} (R_{D1} R_{D2} C_{D1} C_{D2})^2}{(g_{m2} + g_{m3}) (R_{D1} C_{D1} + R_{D2} C_{D2}) C_{D1} C_{D2} C_L} \right] \\

- 10 \log \left[ 1 + \frac{(g_{m2} + g_{m3}) (R_{D1} C_{D1} + R_{D2} C_{D2}) C_C^2}{2g_{mC} g_{m2} g_{m3} g_{m4} (R_{D1} R_{D2})^2 C_{D1} C_{D2} C_L} \right].

\end{array}$$

(14)

As deduced from (14), the stability will not be compromised by GM at large  $C_L$  values, for the trend is rising when  $C_L$  approaches infinity

$$\lim_{C_L \to \infty} GM = 20 \log \left( \frac{2g_{mC}}{g_{m1}g_{m2}g_{m3}g_{m4}R_1R_2R_3C_C} C_L \right)$$

(15)

with refer to PM definition, it can be formulated as

$$PM \approx 90^{\circ} - \tan^{-1} \left[ \frac{GBW}{\omega_0 Q \left( 1 - GBW^2 / \omega_0^2 \right)} \right] + \tan^{-1} \left( \frac{GBW}{z_1} \right) - \tan^{-1} \left( \frac{GBW}{|z_2|} \right). \quad (16)$$

Substituting from (4) to (7) and after some algebra, the above relation can be expanded to (17), as shown at the bottom of the next page.

Tending  $C_L$  to infinity, we get

$$\lim_{C_L \to \infty} PM = 90^{\circ} - \tan^{-1} \left[ \frac{g_{m1}(g_{m2} + g_{m3})R_1R_2R_3C_{D1}C_{D2}}{(R_{D1}C_{D1} + R_{D2}C_{D2})C_C} \right].$$

(18)

In view of (18), it becomes evident that proper sizing of (10)  $C_{D1}$ ,  $C_{D2}$ ,  $R_{D1}$ , and  $R_{D2}$  leads up to adequately high PM in very heavy CLs. In this sense, while zeros are nearly unaffected by the load, increasing  $C_L$  influences the GBW and

asymptotically the GBW decrease compensates the reduction in the high-frequency poles, which finally become real and separate (one pole remains asymptotically constant while the other falls with  $C_L$  at the same rate as GBW). The lower limit of  $C_L$  would not be limited by PM for a carefully sized compensation network, since tending  $C_L$  to zero ends up to

$$\lim_{C_L \to \infty} PM = 90^{\circ} + \tan^{-1} \left[ \frac{g_{m1} R_{D1} R_{D2} C_{D1} C_{D2}}{(R_{D1} C_{D1} + R_{D2} C_{D2}) C_C} \right] - \tan^{-1} \left[ \frac{g_{m1} (g_{m2} + g_{m3})}{2g_{mC} g_{m2} g_{m3} g_{m4} R_{D1} R_{D2}} \right].$$

(19)

Decreasing  $C_L$  raises  $\omega_0$  as is apparent from (4), yielding a higher PM when its effect outperforms the GBW increase in (17). Instead of the PM, the GM dictates the stability conditions under the light CLs, as reducing  $C_L$  is accompanied by compromised stability in the internal Miller loop which causes a peaking in the frequency response [35]. Minimum GM usually happens at maximum Q factor  $(Q_{\text{max}})$  in the minimum load capacitor  $(C_{L\text{min}})$ , which would be equivalent to  $Q_{\text{max}} = \omega_0/\text{GBW}$  if the contribution of the zeros in (14) was neglected. Regarding this scenario, a maximum  $Q_{\text{max}}$  may be set in (5) to evaluate  $C_{L\text{min}}$  as

$$C_{L,\min} \approx \frac{g_{m2}g_{m3}g_{m4}(R_{D1}C_{D1} + R_{D2}C_{D2})C_C^2}{2g_{mC}(g_{m2} + g_{m3})C_{D1}C_{D2}Q_{\max}^2}.$$

(20)

The minimum  $C_L$  is dependent on  $R_{D1}$  and  $R_{D2}$  rather than the output resistors and can be lowered either by increasing  $g_{mC}$  of the cascode devices or by reducing  $R_{D1}$  and  $R_{D2}$ , the former being at the cost of increased power consumption while the latter comes at the price of compromised PM at higher  $C_L$  due to a large  $z_1$  frequency (6).

## B. Design Guidelines

The transfer function along with the derived equations for PM and GM were used to develop an iterative design procedure based on targeted bandwidth and stability margins over a prescribed  $C_L$  range. For this purpose, the parasitics were extracted and updated with the help of computer simulation at the beginning of each sizing sequence. Starting from the transconductance values, a primitive  $g_{m1}$  value needs to be calculated following the design specifications that take into account the input-referred noise, matching, and, most importantly, the  $g_m/I_D$  ratio based on the power, area, and speed envelopes [36]. A maximum GBW, i.e.,  $GBW_{max} = g_{m1}/C_C$  can be evaluated afterward through a maximum GBW limited

by  $C_{L,\min}$  when the feedback factor is set to unity, since the final PM and GM would be large enough to support such approximation. With the GBW<sub>max</sub> acquired, an initial  $C_C$  can be achieved from  $g_{m1}$ . The transconductor  $g_{mC}$  can be subsequently achieved from  $g_{m1}$ , by observing that critical stability margins happen at  $C_{L,\min}$ , so careful placement of poles and zeros is a prerequisite here. Pertinently, the minimum GM can be estimated from (14) as

$$GM_{\min} \approx 20\log\left(\frac{2g_{mC}}{g_{m1}}\right) - 10\log\left[1 + \left(\frac{\omega_{0,\max}}{z_1}\right)^2\right] - 10\log\left[1 + \left(\frac{\omega_{0,\max}}{z_2}\right)^2\right]$$

(21)

where  $\omega_{0,\max}$  is the maximum pole-pair frequency measured from (4) for  $C_{L,\min}$ . The  $g_{mC}/g_{m1}$  ratio must be selected carefully for GM<sub>min</sub> not to become negative in any process-voltage-temperature (PVT) corners. Setting  $g_{mC}=\alpha g_{m1}$  and picking, e.g.,  $\alpha=4$  gives 18 dB by the first term, a fairly sufficient margin to counteract the adverse contributions of the second and the third terms caused by the zeros. Sizing  $g_{m2}$ ,  $g_{m3}$ , and  $g_{m4}$  is the next step and should rely on the designated operating regions and the relevant power/area trade-offs.

The resistors  $R_{D1}$  and  $R_{D2}$  are then sized based on the proper location of the zeros. Placing the first zero right after the maximum GBW frequency, i.e.,  $\gamma \times \text{GBW}_{\text{max}}$  which happens at  $C_{L,\text{min}}$ , we get

$$z_{1} = \gamma \cdot GBW_{\text{max}} \Rightarrow \frac{1}{R_{D1}C_{D1}} + \frac{1}{R_{D2}C_{D2}}$$

$$= \gamma \cdot GBW_{\text{max}}. \tag{22}$$

The second RHP zero,  $z_2$ , should be positioned well beyond GBW<sub>max</sub> simultaneously. Choosing  $|z_2| > 10$  GBW<sub>max</sub> would be a safe margin for the phase contribution of  $z_2$  not to disturb the frequency response, consequently

$$z_2 > 10 \cdot \text{GBW}_{\text{max}} \Rightarrow R_{D1}R_{D2} > 5 \frac{g_{m2} + g_{m3}}{\alpha g_{m2}g_{m3}g_{m4}}.$$

(23)

The sizing of  $C_{D1}$  and  $C_{D2}$  is relied on  $R_{D1}C_{D1} + R_{D2}C_{D2}$ , the term that contributes directly to the absolute PM and its limits derived in (18) and (19). Larger  $C_{D1}$  and  $C_{D2}$  improve the PM but also add to the silicon footprint and vice-versa. After setting  $C_{D1}$  and  $C_{D2}$ , the next step is to modify the initial  $g_{m1}$  and the consequent  $C_C$  and  $g_{mC}$ . To estimate the required  $C_C$ , we set  $\omega_{0,\max}$  equal to  $\beta \cdot \text{GBW}_{\max}$  and choose  $\beta$  between

$$PM = 90^{\circ} - \tan^{-1} \left\{ \frac{g_{m1}(g_{m2} + g_{m3})R_{1}R_{2}R_{3}C_{D1}C_{D2}C_{L}}{C_{C} \left[ \frac{(g_{m2}g_{m3}g_{m4}R_{1}R_{2}R_{3}C_{C} + C_{L})(R_{D1}C_{D1} + R_{D2}C_{D2})}{2g_{mC}(g_{m2}g_{m3}g_{m4}R_{1}R_{2}R_{3}C_{C} + C_{L})} \right] \right\}$$

$$+ \tan^{-1} \left( \frac{g_{m1}g_{m2}g_{m3}g_{m4}R_{D1}R_{D2}R_{1}R_{2}R_{3}C_{C} + C_{L})}{(g_{m2}g_{m3}g_{m4}R_{1}R_{2}R_{3}C_{C} + C_{L})(R_{D1}C_{D1} + R_{D2}C_{D2})} \right)$$

$$- \tan^{-1} \left( \frac{g_{m1}(g_{m2} + g_{m3})R_{1}R_{2}R_{3}C_{C}}{2g_{mC}g_{m2}g_{m3}g_{m4}R_{D1}R_{D2}R_{1}R_{2}R_{3}C_{C}} \right)$$

$$(17)$$

2 and 3 to allow for sufficient GM and PM. Combining (8) with (4), we get

$$C_C = \beta g_{m1} \sqrt{\frac{(g_{m2} + g_{m3})C_{D1}C_{D2}C_{L,\text{min}}}{2g_{mC}g_{m2}g_{m3}g_{m4}(R_{D1}C_{D1} + R_{D2}C_{D2})}}.$$

(24)

Substituting  $g_{mC} = \alpha g_{m1}$  from the former assumptions,  $C_C$  will befound by

$$C_C = \frac{\beta}{\alpha} \sqrt{\frac{g_{mC}(g_{m2} + g_{m3})C_{D1}C_{D2}C_{L,\text{min}}}{2g_{m2}g_{m3}g_{m4}(R_{D1}C_{D1} + R_{D2}C_{D2})}}.$$

(25)

Combining (22) and (24), the coefficients  $\alpha$ ,  $\beta$ , and  $\gamma$  need to be adjusted such that a sufficiently high  $GM_{min}$  is resulted from the following equation:

$$GM_{min} \approx 20log(2\alpha) - 10log \left\{ \left[ 1 + \left( \frac{\beta}{\gamma} \right)^2 \right] \left[ 1 + \left( \frac{\beta}{10} \right)^2 \right] \right\}.$$

(26)

The above procedure should be reiterated and enriched by simulations as the initial assessments of the parasitics and some design parameters are not accurate. Simulation of the zeros and poles under the component and process variations would be also necessary in the final phase. A prototype of the proposed OTA was realized by taking into account the described design rules, using an algorithm that optimizes the device sizes for lesser power consumption and area. Measurement and simulation results are discussed in Section IV.

## IV. RESULTS

# A. Simulation Results

The operation of the proposed amplifier was analyzed through the simulation results in a 65-nm standard CMOS process under a 1.2-V voltage supply. Optimizations were conducted according to the design guidelines in Section III to reach a stable operation with maximum bandwidth over a 5–100 nF  $C_L$  range. The final configuration consumes 140  $\mu$ A current in a total area of 0.0086 mm<sup>2</sup>. Table I outlines the transistor sizes and the small-signal parameters. Notably, the value of  $g_{mC}$  was set to  $4g_{m1}$  in line wirh the design guidelines described in the previous section. Table II presents the operation details for  $C_L=5$  nF. The GBW product was adjusted to 5 MHz in this case, while the minimum GM is derived as 9 dB thanks to  $\alpha=4$  as discussed earlier.

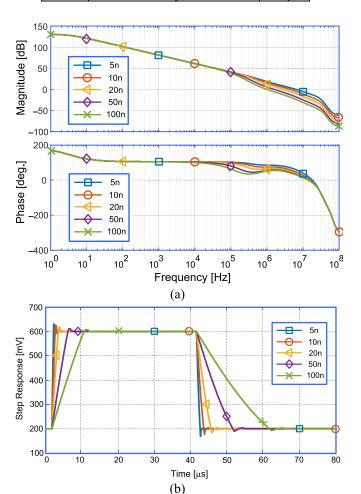

Fig. 4(a) shows the loop-gain frequency responses at various load capacitors. The main pole depends on the Miller capacitors for small  $C_L$  values, becoming a function of the load capacitor for heavy  $C_L$ s. Fig. 4(b) presents the step response of the amplifier in buffer configuration to the falling and rising edges of a 400-mV input. The supply current drawn by the output stage lies in the almost zero to some mA range depending on the step size and  $C_L$ , while the bias current of the output stage indicates a tolerance of  $\pm 12\%$  and  $\pm 8\%$  across the 0.2–0.6 V output voltage and 1.2–1.5 V supply voltage ranges, respectively.

The OTA is found to be stable with adequately high stability margins over the designative  $C_L$  range from 5 nF to infinity,

TABLE I

TRANSISTOR SIZES, SMALL-SIGNAL PARAMETERS, AND PASSIVE COMPONENTS VALUES

| Stage #   | Transistor                    | W/L                             | Param.    | Value                  |

|-----------|-------------------------------|---------------------------------|-----------|------------------------|

| 1         | $\frac{M_0}{M_1 - M_2}$       | 64.1 μ / 0.5 μ<br>8.5 μ / 0.3 μ |           | 81μA/V                 |

|           | $M_3 - M_4$                   | 52.3 μ / 1.7 μ                  | $g_{m1}$  |                        |

|           | $\frac{M_5 - M_6}{M_7 - M_8}$ | 6.3 μ / 0.2 μ<br>36.3 μ / 0.2 μ | $g_{mc}$  | 340μA/V                |

|           | $M_9 - M_{10}$                | 2.9 μ / 0.3 μ                   |           |                        |

| 2         | $M_{11}$                      | 2.3 μ / 0.4 μ                   | a         | 56μA/V                 |

|           | $M_{12}$                      | 20.0 μ/1.7 μ                    | $g_{m_2}$ |                        |

| 3         | $M_{13}$                      | 12.8 μ/1.7 μ                    | $g_{m3}$  | 114μA/V                |

|           | $M_{14}$                      | 4.4 μ / 0.5 μ                   | $g_{mf1}$ | 95μA/V                 |

| 4         | $M_{15}$                      | 9.6 μ / 0.2 μ                   | $g_{m4}$  | 1.2mA/V                |

|           | $M_{16}$                      | 40.8 μ / 0.2 μ                  | $g_{mf2}$ | 1.6 mA/V               |

|           |                               | $C_{D1}$                        |           | 0.4 pF                 |

| Comp.     |                               | $R_{D1}$                        |           | $700~\mathrm{k}\Omega$ |

|           | $C_{D2}$                      |                                 |           | 0.6 pF                 |

| IICC WOLK |                               | $\frac{R_{D2}}{C_C}$            |           | $500 \text{ k}\Omega$  |

|           |                               | 2.0 pF                          |           |                        |

Fig. 4. Simulated performance for different  $C_L$  values. (a) Open-loop frequency response. (b) Unity-gain Settling response  $\times 10$ .

becoming gradually unstable for lighter CL due to insufficient GM. The stability is typically limited by GM rather than PM in lighter  $C_L$ s. Nevertheless, it is possible to configure the compensation network for the proposed OTA such that it drives

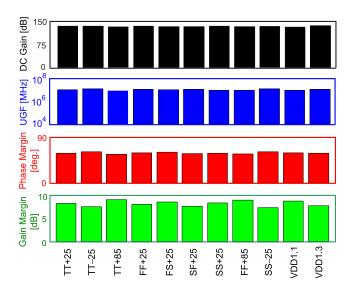

Fig. 5. Performance comparison in different process corners for  $C_L = 5$  nF.

$\label{eq:table II} \text{Design Parameters for the Nominal } C_L = 5 \text{ nF}$

| Voltage Supply [V]     | 1.20  |

|------------------------|-------|

| Quiescent Current [μA] | 140   |

| DC Gain [dB]           | 130   |

| UGF [MHz]              | 5.15  |

| PM [deg.]              | 58.11 |

| GM [dB]                | 8.86  |

the more common on-chip loads. For instance, reducing the original  $C_C$ ,  $R_{D1}$ , and  $R_{D2}$  into 0.7 pF, 68 k $\Omega$ , and 12 k $\Omega$  extends the lower  $C_L$  limit to as low as 5 pF consistent with the results from (20). The maximum  $C_L$  limit, however, drops to around 250 pF because of the additional phase lag caused by the second term in (18) which negates the PM.

#### B. Corner and Monte-Carlo Analysis

Corner and Monte-Carlo simulations were executed to investigate the immunity of the design against local and systematic variations. Fig. 5 illustrates the loop-gain parameters in the minimum  $C_L$  of 5 nF, which takes into account the realistic deviations of the voltage supply ( $\pm 5\%$ ) and temperature (-25 °C to 85 °C) across the TT = typical, SS = slow nMOS, slow pMOS, FF = Fast nMOS, and Fast pMOS process corners. Table III lists the worst and the best cases of each parameter. The design was found to be stable in different process, voltage, and temperature corners, and the GBW and dc gain distributions were acceptable.

Monte-Carlo simulation results (1000 runs) are summarized in Table IV for the nominal CL of  $C_L = 5$  nF. The mean values are slightly different from the simulated design parameters set. The standard deviation is contained for each parameter with a maximum coefficient of deviation ( $\sigma/\mu$ ), registered for the unity-gain frequency (UGF), approximately equal to 3.5%.

## C. Measurement Results and Comparisons

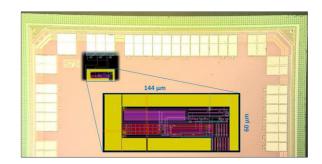

The proposed OTA with the chip micrograph shown in Fig. 6 was designed in a standard 65-nm CMOS. The exper-

TABLE III

BEST AND WORST PARAMETERS OVER CORNERS

| Parameter    | Value     | Corner      |  |

|--------------|-----------|-------------|--|

| Min. UGF     | 4.47 MHz  | TT (+85°C)  |  |

| Min. PM      | 56.04 °   | TT (+85°C)  |  |

| Min. GM      | 7.91 dB   | SS (-25°C)  |  |

| Min. DC Gain | 127.90 dB | VDD = 1.1 V |  |

| Max. UGF     | 6.15 MHz  | SS (-25°C)  |  |

| Max. PM      | 60.94 °   | SS (-25°C)  |  |

| Max. GM      | 9.74 dB   | TT (+85°C)  |  |

| Max. DC Gain | 131.9 dB  | VDD = 1.3 V |  |

$\label{eq:table_iv} \text{TABLE IV}$  Summary of Monte-Carlo Analysis (1000 Runs @  $C_L = 5 \text{ nF}$ )

| Parameter                            | μ     | $\sigma$ |

|--------------------------------------|-------|----------|

| UGF [MHz]                            | 5.164 | 0.18     |

| <i>PM</i> [deg.]                     | 58.19 | 0.90     |

| GM [dB]                              | 10.04 | 0.24     |

| $I_{DD}\left[ \mu \mathrm{A}\right]$ | 134.6 | 3.80     |

| SR [mV/μs]                           | 429.3 | 1.46     |

Fig. 6. Chip microphotograph.

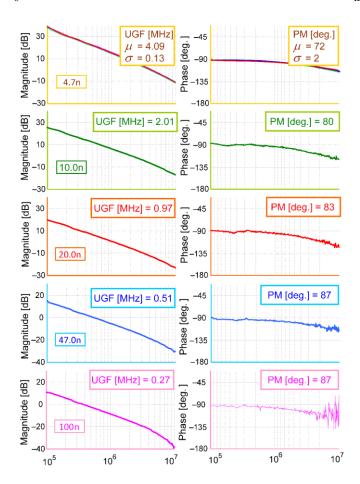

imental setup, not depicted for its standard arrangement, includes double power suppliers besides a waveform generator and the characterization is performed on seven samples with bond-wire. An oscilloscope, Tektronix TDS5054B, was utilized to examine the transient output and input responses. To measure the frequency response, an E5061B LF-RF network analyzer (ENA) from Keysight Technologies was also employed. Fig. 7 illustrates the measured open-loop gain frequency responses for  $C_L$  ranging between 4.7 and 100 nF. Above 100 dB dc gain was measured with the UGF frequency of about 4.09 and 0.27 MHz and a PM of 72° and 87° at 4.7 and 100 nF loads, respectively, owing to the UGF being scaled by  $C_L$ , as predicted by (8).

The measured UGF turns out to be less than about 21% as compared to their nominal values, which is surely attributed to the internal parasitics as well as the layout-dependent effects. For instance, metal-oxide-metal (MOM) and high sheet-resistance capacitors and resistors were used in the compensation network, respectively. Such components, however, suffer from high process excursions, especially for the MOM case, being about 25%–30% of variations, but have been

Fig. 7. Measured loop-gain frequency response at different  $C_L$ .

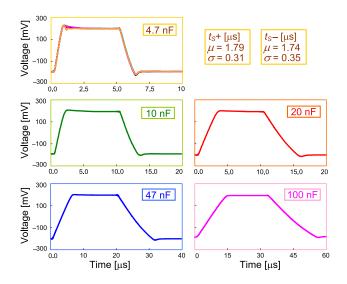

Fig. 8. Measured loop-gain frequency response at different  $C_L$ .

exploited for more compactness and lower equivalent series resistance (ESR).

Fig. 8 exhibits the step response of the unity-gain OTA subject to an input step size of 400 mV. As for  $C_L=4.7$  nF, the mean( $\mu$ ) positive and negative 1% settling times are 1.79 and 1.74  $\mu$ s with a standard deviation ( $\sigma$ ) of 0.31 and 0.35  $\mu$ s, respectively.

TABLE V Comparison With Three-Stage OTAs

| This work   | [26]    | [25]      | [37]    | [9]    |                                   |

|-------------|---------|-----------|---------|--------|-----------------------------------|

| Tills WOLK  | 2020    | 2018      | 2016    | 2013   |                                   |

| 65          | 130     | 350       | 350     | 350    | Tech. [nm]                        |

| 4           |         | 3         |         |        | #stages                           |

| 0.0086      | 0.006   | 0.0025    | 0.003   | 0.016  | Area [mm <sup>2</sup> ]           |

| 138.2       | 185     | 6.36      | 24.9    | 72     | $I_{DD}[\mu A]$                   |

| 132a        | 71.25   | 113       | >100    | >100   | $A_0$ [dB]                        |

| 4.7-100     | 4.45-50 | 5-100     | 5–15    | 1-15   | $C_L[nF]$                         |

| 3           | 0       | 0.5       | 1       | 2.6    | $C_T$ [pF]                        |

| 20          | 11.24   | 20        | 3       | 15     | $C_{L,max}/C_{L,mix}$             |

| 4.1-        | 5.41-   | 2.88-     | 2.85-   | 3.37-  |                                   |

| 0.27        | 0.46    | 0.43      | 2.38    | 0.95   | UGF [MHz]                         |

| 0.53-0.03 a | 0.49-   | 0.36-     | 0.76-   | 0.59-  | CD[W/well                         |

|             | 0.04    | 0.045     | 0.3     | 0.22   | $SR[V/\mu s]$                     |

| 72–87       | 69–90   | 46–59     | 78–47   | 83-52  | PM [deg.]                         |

| 1 77 16     | 0.57-   | 2.05–7.7  | 0.63-   | 1.28-  | 1% t <sub>S</sub> [μs]            |

| 1.77–16     | 4.62    |           | 0.93    | 4.49   |                                   |

| 195.37      | 124.3   | 6'761     | 1'433.7 | 198    | IFOM <sub>S</sub> <sup>(1)</sup>  |

| 25.99       | 10.81   | 707.6     | 180.7   | 45.8   | IFOM <sub>L</sub> <sup>(2)</sup>  |

| 22'717      | 20'721  | 2'704'403 | 482.7   | 12'370 | IFOM <sub>SA</sub> <sup>(3)</sup> |

| 3'022       | 1'801   | 283'019   | 60.8    | 2'865  | IFOM <sub>LA</sub> <sup>(4)</sup> |

a:minimum value

TABLE VI COMPARISON WITH FOUR-STAGE OTAS

|                                   | [38]<br>2008 | [39] <sup>b</sup><br>2014 | [32]<br>2015 | [30]<br>2020 | This work  |

|-----------------------------------|--------------|---------------------------|--------------|--------------|------------|

| Tech. [nm]                        | 120          | 65                        | 350          | 130          | 65         |

| Area [mm <sup>2</sup> ]           | 0.017        |                           | 0.014        | 0.007        | 0.0086     |

| $I_{DD}[\mu A]$                   | 1400         | 80                        | 52           | 146          | 138.2      |

| $A_0$ [dB]                        | 108          | 91                        | 173ª         | 107          | 132a       |

| $C_L[nF]$                         | 0.5          | 1                         | 0.33-1       | 0.4-10       | 4.7-100    |

| $C_T$ [pF]                        | 17.6         | 1                         | 9.7          | 3.1          | 3          |

| UGF [MHz]                         | 40.2         | 19.06                     | 2.98         | 2.75-1.18    | 4.1-0.27   |

| SR [V/µs]                         | 17.52        | 1.45                      | 1.18         | 0.92-0.14    | 0.53-0.03a |

| PM [deg.]                         | 62           | 59                        | 55           | 48–61        | 72–87      |

| 1% t <sub>S</sub> [μs]            | 0.14         | 0.33                      | 0.46         | 0.33-9.75    | 1.77-16    |

| IFOM <sub>S</sub> <sup>(1)</sup>  | 14.36        | 238.25                    | 57.31        | 97           | 195.37     |

| IFOM <sub>L</sub> <sup>(2)</sup>  | 6.26         | 18.13                     | 22.69        | 11.51        | 25.99      |

| IFOM <sub>SA</sub> <sup>(3)</sup> | 845          |                           | 4'093        | 13'855       | 22'717     |

| IFOM <sub>LA</sub> <sup>(4)</sup> | 368          |                           | 1'621        | 1'644        | 3'022      |

a:minimum value

The positive/negative SR+/SR- were measured as 0.65/0.53 and 0.05/0.03 V/ $\mu$ s for 4.7 and 100 nF CLs, respectively. Altogether, the step responses demonstrate very close agreement with the simulation results. A longer settling time was, however, appreciated owing to the aforementioned internal parasitics and layout dependent effect as well as the loading of the bond wires and the experiment setup.

The figures of merit, IFOM<sub>S</sub> = GBW ×  $C_{L,max}/I_{DD}$  and IFOM<sub>L</sub> = SR ×  $C_{L,max}/I_{DD}$ , were employed to quantify the small-signal and large-signal characteristics in the upper limit of  $C_L$ , whereas IFOM<sub>SA</sub> = IFOM<sub>S</sub>/Area and IFOM<sub>LA</sub> = IFOM<sub>L</sub>/Area were added to include the active area [2]. Tables V and VI compare the performance metrics of the proposed amplifier with some of the state-of-the-art three- and four-stage OTAs based on the above FOMs. The minimum among SR+/SR- is reported for each  $C_L$  and is used later to find the large-signal FOMs.

b:simulated results

The proposed four-stage OTA does not outperform all the other solutions among the three-stage OTAs driving a wide  $C_L$  range, which is mainly due to the increased number of gain stages and a more complicated compensation network.

However, among the fabricated and tested four-stage amplifiers, it outperforms all the topologies presented in Table VI when taking into consideration the active area, consuming current, range of stability, as well as the large- and small-signal operations. The proposed OTA can drive the widest  $C_L$  range up to 100 nF for analogous current consumption and compensation capacitor sizes.

#### V. CONCLUSION

The principle of hybrid-cascode frequency compensation was applied to a four-stage feedback amplifier, thus leading up to improved performance metrics with respect to the prior art. Other than the local Miller compensations used for the stability of inner gain stages, two Miller capacitors with current buffers are applied according to the idea. A reliable operation and a wide range of the CLs spanning from 4.7-nF up to infinity were achieved by shaping the frequency response such that stability is ensured initially by the Miller and, gradually, by the load capacitor in lower and higher CLs, respectively. The proposed amplifier was fabricated in a 65-nm CMOS, consuming  $168~\mu W$  power while occupying an active area of  $0.0086~\rm mm^2$ . Experimental results indicate a gain factor higher than  $100~\rm dB$ , and a PM of at least  $72^\circ$  for the CLs beyond  $4.7-\rm nF$ .

# REFERENCES

- [1] W. Sansen, "1.3 analog CMOS from 5 micrometer to 5 nanometer," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 1–6.

- [2] H. Aminzadeh, A. Ballo, and A. D. Grasso, "Frequency compensation of three-stage OTAs to achieve very wide capacitive load range," *IEEE Access*, vol. 10, pp. 70675–70687, 2022.

- [3] M. A. Mohammed and G. W. Roberts, "Generalized relationship between frequency response and settling time of CMOS OTAs: Toward many-stage design," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 12, pp. 4993–5006, Dec. 2021.

- [4] K. Nang Leung and P. K. T. Mok, "Analysis of multistage amplifier-frequency compensation," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 48, no. 9, pp. 1041–1056, Sep. 2001.

- [5] J. Riad, J. J. Estrada-López, and E. Sánchez-Sinencio, "Classification and design space exploration of low-power three-stage operational transconductance amplifier architectures for wide load ranges," *Elec*tronics, vol. 8, no. 11, p. 1268, Nov. 2019.

- [6] S. G. Brantley and V. V. Ivanov, "Compensation circuitry and method for amplifiers driving large capacitive loads," U.S. Patent 2014/0 218 112 A1, Aug. 7, 2014.

- [7] A. D. Grasso, G. Palumbo, and S. Pennisi, "Dual push-pull high-speed rail-to-rail CMOS buffer amplifier for flat-panel displays," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 12, pp. 1879–1883, Dec. 2018.

- [8] H. Aminzadeh, "Study of capacitance nonlinearity in nano-scale multistage MOSFET-only sigma-delta modulators," AEU, Int. J. Electron. Commun., vol. 85, pp. 150–158, Feb. 2018.

- [9] Z. Yan, P.-I. Mak, M.-K. Law, and R. P. Martins, "A 0.016-mm<sup>2</sup> 144-μW three-stage amplifier capable of driving 1-to-15 nF capacitive load with >0.95-MHz GBW," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 527–540, Feb. 2013.

- [10] H. Aminzadeh, R. Lotfi, and K. Mafinezhad, "Low-dropout voltage reference: An approach to low-temperature-sensitivity architectures with high drive capability," *Electron. Lett.*, vol. 45, no. 24, p. 1200, 2009.

- [11] H. Khorramabadi, "A CMOS line driver with 80-dB linearity for ISDN applications," *IEEE J. Solid-State Circuits*, vol. 27, no. 4, pp. 539–544, Apr. 1992.

- [12] A. Paul, J. Ramírez-Angulo, A. D. Sánchez, A. J. López-Martín, R. G. Carvajal, and F. X. Li, "An enhanced gain-bandwidth class-AB Miller op-amp with 23,800 MHz·pF/mW FOM, 11–16 current efficiency and wide range of resistive and capacitive loads driving capability," *IEEE Access*, vol. 9, pp. 69783–69797, 2021.

- [13] C. Mohan and P. M. Furth, "A 16-Ω audio amplifier with 93.8-mW peak load power and 1.43-mW quiescent power consumption," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 59, no. 3, pp. 133–137, Mar. 2012.

- [14] Z. Yan, P.-I. Mak, M.-K. Law, R. P. Martins, and F. Maloberti, "Nested-current-mirror rail-to-rail-output single-stage amplifier with enhancements of DC gain, GBW and slew rate," *IEEE J. Solid-State Circuits*, vol. 50, no. 10, pp. 2353–2366, Oct. 2015.

- [15] S.-W. Hong and G.-H. Cho, "A pseudo single-stage amplifier with an adaptively varied medium impedance node for ultra-high slew rate and wide-range capacitive-load drivability," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 10, pp. 1567–1578, Oct. 2016.

- [16] Z. Yan, P.-I. Mak, and R. P. Martins, "Two stage operational amplifiers: Power and area efficient frequency compensation for driving a wide range of capacitive load," *IEEE Circuits Syst. Mag.*, vol. 11, no. 1, pp. 26–42, 1st Quart., 2011.

- [17] M. Ho et al., "A two-stage large-capacitive-load amplifier with multiple cross-coupled small-gain stages," *IEEE Trans. Very Large Scale Integr.* (VLSI) Syst., vol. 24, no. 7, pp. 2580–2592, Jul. 2016.

- [18] R. G. H. Eschauzier, L. P. T. Kerklaan, and J. H. Huijsing, "A 100-MHz 100-dB operational amplifier with multipath nested Miller compensation structure," *IEEE J. Solid-State Circuits*, vol. 27, no. 12, pp. 1709–1717, 1992.

- [19] K. N. Leung, P. K. T. Mok, W.-H. Ki, and J. K. O. Sin, "Three-stage large capacitive load amplifier with damping-factor-control frequency compensation," *IEEE J. Solid-State Circuits*, vol. 35, no. 2, pp. 221–230, Feb. 2000.

- [20] F. You, S. H. Embabi, and E. Sanchez-Sinencio, "Multistage amplifier topologies with nested G<sub>m</sub>-C compensation," *IEEE J. Solid-State Cir*cuits, vol. 32, no. 12, pp. 2000–2011, Dec. 1997.

- [21] H. Aminzadeh, "Three-stage nested-Miller-compensated operational amplifiers: Analysis, design, and optimization based on settling time," *Int. J. Circuit Theory Appl.*, vol. 39, no. 6, pp. 573–587, Jun. 2011.

- [22] X. Fan, C. Mishra, and E. Sanchez-Sinencio, "Single Miller capacitor frequency compensation technique for low-power multistage amplifiers," *IEEE J. Solid-State Circuits*, vol. 40, no. 3, pp. 584–592, Mar. 2005.

- [23] M. Tan and W.-H. Ki, "A cascode Miller-compensated three-stage amplifier with local impedance attenuation for optimized complex-pole control," *IEEE J. Solid-State Circuits*, vol. 50, no. 2, pp. 440–449, Feb. 2015.

- [24] S. S. Chong and P. K. Chan, "Cross feedforward cascode compensation for low-power three-stage amplifier with large capacitive load," *IEEE J. Solid-State Circuits*, vol. 47, no. 9, pp. 2227–2234, Sep. 2012.

- [25] A. D. Grasso, D. Marano, G. Palumbo, and S. Pennisi, "High-performance three-stage single-Miller CMOS OTA with no upper limit of CL," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 11, pp. 1529–1533, Nov. 2018.

- [26] J. Riad, J. J. Estrada-López, I. Padilla-Cantoya, and E. Sánchez-Sinencio, "Power-scaling output-compensated three-stage OTAs for wide load range applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 7, pp. 2180–2192, Jul. 2020.

- [27] K. H. Mak et al., "A 0.7 V 24 μA hybrid OTA driving 15 nF capacitive load with 1.46 MHz GBW," *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2750–2757, Nov. 2015.

- [28] H. Aminzadeh and A. Dashti, "Hybrid cascode compensation with current amplifiers for nano-scale three-stage amplifiers driving heavy capacitive loads," *Anal. Integr. Circuits Signal Process.*, vol. 83, no. 3, pp. 331–341, Jun. 2015.

- [29] H. Aminzadeh, M. Danaie, and W. A. Serdijn, "Hybrid cascode feedforward compensation for nano-scale low-power ultra-area-efficient three-stage amplifiers," *Microelectron. J.*, vol. 44, no. 12, pp. 1201–1207, Dec. 2013.

- [30] S. A. Fordjour, J. Riad, and E. Sánchez-Sinencio, "A 175.2-mW 4-stage OTA with wide load range (400 pF-12 nF) using active parallel compensation," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 28, no. 7, pp. 1621–1629, Jul. 2020.

- [31] M. A. Mohammed and G. W. Roberts, "Scalable multi-stage CMOS OTAs with a wide CL-drivability range using low-frequency zeros," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 70, no. 1, pp. 74–87, Jan. 2023.

- [32] A. D. Grasso, G. Palumbo, and S. Pennisi, "High-performance four-stage CMOS OTA suitable for large capacitive loads," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 10, pp. 2476–2484, Oct. 2015.

- [33] P. Manikandan, "Miller compensated four-stage OTA with Q-reduction for wide range of load capacitors," *Microelectron. J.*, vol. 128, Oct. 2022, Art. no. 105538.

- [34] H. Aminzadeh, A. D. Grasso, and G. Palumbo, "A methodology to derive a symbolic transfer function for multistage amplifiers," *IEEE Access*, vol. 10, pp. 14062–14075, 2022.

- [35] W. Qu, S. Singh, Y. Lee, Y.-S. Son, and G.-H. Cho, "Design-oriented analysis for Miller compensation and its application to multistage amplifier design," *IEEE J. Solid-State Circuits*, vol. 52, no. 2, pp. 517–527, Feb. 2017.

- [36] H. Aminzadeh, "Systematic circuit design and analysis using generalised g<sub>m</sub>/I<sub>D</sub> functions of MOS devices," *IET Circuits, Devices Syst.*, vol. 14, no. 4, pp. 432–443, 2020.

- [37] D. Marano, A. D. Grasso, G. Palumbo, and S. Pennisi, "Optimized active single-Miller capacitor compensation with inner half-feedforward stage for very high-load three-stage OTAs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 9, pp. 1349–1359, Sep. 2016.

- [38] W. Yan, R. Kolm, and H. Zimmermann, "Efficient four-stage frequency compensation for low-voltage amplifiers," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2008, pp. 2278–2281.

- [39] A. D. Grasso, G. Palumbo, S. Pennisi, and G. Di Cataldo, "High-performance frequency compensation topology for four-stage OTAs," in Proc. 21st IEEE Int. Conf. Electron., Circuits Syst. (ICECS), Dec. 2014, pp. 211–214.

Alfio Dario Grasso (Senior Member, IEEE) was born in Catania, Italy, in 1978. He received the Laurea degree (summa cum laude) and the Ph.D. degree in electronic engineering from the University of Catania, Catania, in 2003 and 2006, respectively.

From 2006 to 2011, he worked as a Freelance Engineer in the field of electronic systems. From 2009 to 2010, he was an Adjunct Professor of electronics with the Kore University of Enna, Enna, Italy. In 2011, he became a Researcher (an Assistant Professor) with the University of Catania,

where he was appointed as an Associate Professor, in 2015. In 2017, he received the Italian National Scientific Qualification for the position of a Full Professor. He teaches graduate courses on advanced VLSI digital design, microelectronics, and basic electronics. He has coauthored more than 120 papers on referred international journals and conference proceedings. His current research interests include low-voltage low-power analog circuit design and analog and mixed signal processing for energy harvesting applications.

Prof. Grasso is a member of the Editorial Board of MDPI Sensors. He is an Associate Editor of the IET *Electronics Letters* and the Wiley *International Journal of Circuits Theory and Applications*.

**Hamed Aminzadeh** (Member, IEEE) received the M.S. and Ph.D. degrees in electronics engineering from Payame Noor University, Tehran, Iran, in 2008 and 2010, respectively.

From 2010 to 2014, he was with the Delft University of Technology, Delft, The Netherlands, where he worked on low-voltage power regulation techniques for biomedical implanted devices. Since 2012, he has been with Payame Noor University, where he is currently an Associate Professor. He has coauthored more than 50 articles on international journals and

conference proceedings. His current research interests include modeling and optimization of analog circuits for low-voltage IoT and biomedical devices, and low-power digital-to-analog and analog-to-digital converters design for telecommunication applications.

Mohammad M. Valinezhad (Member, IEEE) was born in Mashhad, Iran, in 1995. He received the B.S. degree (Hons.) in electrical electronics engineering and the M.S. degree from Payame Noor University (PNU), Tehran, Iran, in 2017 and 2019, respectively.

His research interests include low-power, low-voltage analog integrated circuits designed for biomedical applications, voltage and current references, and frequency compensation solutions for operational amplifiers. He is presently active in developing computer-aided design tools for analog

integrated circuits applications.

Andrea Ballo (Member, IEEE) was born in Catania, Italy, in 1990. He received the Laurea degree (summa cum laude) and the Ph.D. degree in electronic engineering from the University of Catania, Catania, in 2016 and 2020, respectively.

Since 2021, he has been a Research Fellow and an Adjunct Professor of electronic devices with the University of Catania. His current research interests include low-voltage low-power analog circuit design and analog and mixed electronics for energy harvesting applications.

Mohammad Jamali was born in Lorestan, Iran, in 1991. He received the B.S. degree in electrical electronics engineering from Islamic Azad University, Najafabad Branch, Najafabad, Iran, in 2015, and the M.S. degree from Payame Noor University (PNU). Tehran, Iran, in 2019.

His research interests include the design of lowpower, low-voltage integrated circuits and analog integrated filters for medical applications, and the frequency compensation solutions for operational amplifiers.