# Two-Stage OTA with all Subthreshold MOSFETs and Optimum GBW to DC-Current Ratio

J. Beloso-Legarra, *Graduate Student Member*, *IEEE*, A.D. Grasso, *Senior Member*, *IEEE*, A.J. Lopez-Martin, *Senior Member*, *IEEE*, G. Palumbo, *Fellow*, *IEEE*, S. Pennisi, *Fellow*, *IEEE*

Abstract—An approach for the design of two-stage class-AB OTAs with sub-1µA current consumption is proposed and demonstrated. The approach employs MOS transistors operating in subthreshold and allows maximum gain-bandwidth product (GBW) to be achieved for a given DC current budget, by setting optimum distribution of DC currents in the two amplifier stages. Following this strategy, a class AB OTA was designed in a standard 0.5-µm CMOS technology supplied from 1.6-V and experimentally tested. Measured GBW was 307 kHz with 980-nA DC current consumption while driving an output capacitance of 40 pF with an average slew rate of 96 V/ms.

Index Terms—Low power design, subthreshold operation, two-stage amplifier, Miller compensation, CMOS.

# I. INTRODUCTION

The growing interest in wireless sensor networks, biomedical electronics and the Internet of Things [1]-[4], continuously demands for novel CMOS circuits and sub-systems with limited DC current consumption well below one microampere. Among the CMOS analog building blocks, the operational transconductance amplifier (OTA) is one of the most popular thanks to its high versatility so that it is frequently instantiated, even several times, within a single integrated circuit, for the implementation of high-accuracy closed-loop configurations. It is consequently of great importance to find suitable OTA architectures and associated design criteria enabling the optimized exploitation of the limited DC current budget, while preserving performance in terms of gain-bandwidth product (GBW) or, alternatively, settling time.

To this aim, subthreshold operation of MOS transistors has been exploited since 1977 [5] until very recently, where, for instance, inverter-based subthreshold amplifiers have been proposed [6], [7]. However, inverter-based solutions suffer from inaccurate control of the DC current that therefore depends on

Manuscript received October XX, 2021. This work has been partially supported by grant PID2019-107258RB-C32 (AEI).

J. Beloso-Legarra and A. J. López-Martín are with the Institute of Smart Cities, Public University of Navarra, 31006 Pamplona, Spain (e-mail: javier.beloso@unavarra.es, antonio.lopez@unavarra.es).

A.D. Grasso, G. Palumbo and S. Pennisi are with the Dipartimento di Ingegneria Elettrica, Elettronica e Informatica, University of Catania, 95125 Catania, Italy (e-mail: agrasso@dieei.unict.it, gpalumbo@dieei.unict.it, spennisi@dieei.unict.it).

process and supply voltage variations. To reduce current and power consumption, alternative architectures and design techniques have also been conceived like body-driven OTAs [8]-[12], dynamic amplifiers [13] or ring amplifiers [14].

Nevertheless, OTAs based on gate-driven differential pairs remain quite indispensable thanks to their robustness and reliability, qualities that make these solutions the most acceptable by the industry standards [15]-[19]. Of course, reduction of the DC current consumption, especially under high capacitive loads while maintaining adequate slew rate values, mandates for a class AB output stage. An optimized design methodology for three-stage subthreshold OTAs was presented by the authors in [20]. In this paper, this approach is modified for a two-stage OTA, which can be employed in those cases where a lower DC gain is required and/or a reduced DC current consumption.

More specifically, a design approach using a class AB two-stage OTA with all transistors in subthreshold region exploiting Miller frequency compensation with pole-zero cancelation (MCPZC) that maximizes the gain-bandwidth product for a given total current budget is presented in this paper. The approach is discussed in Sec. II and is subsequently exploited in Sec. III to design an amplifier in a standard 0.5-µm CMOS technology. Measurement results confirm the proposed guidelines, revealing an outstanding performance in terms of small and large-signal characteristics as well as current efficiency.

### II. PROPOSED DESIGN STRATEGY

# A. Preliminary Considerations

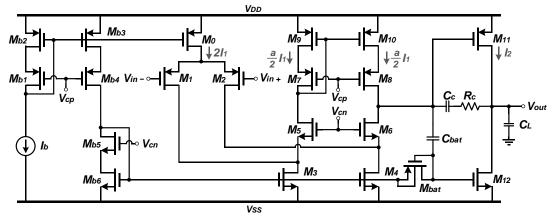

The schematic diagram of the class AB OTA utilized in this paper is depicted in Fig. 1. It is based on a folded-cascode input stage with p-channel source-coupled pair ( $M_0$ - $M_{10}$ ) and a common-source class-AB second stage ( $M_{11}$ - $M_{12}$ ), with  $M_{bat}$  and  $C_{bat}$  providing DC biasing and AC driving for transistor  $M_{12}$ , as a result of the so called quasi-floating gate (QFG) approach [21]-[23]. Transistors  $M_{b1}$ - $M_{b6}$  implement a conventional bias network. For the low current application target, all transistors are biased in subthreshold regime.

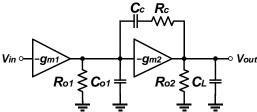

Fig. 2 shows the simplified equivalent small-signal circuit of the OTA where  $g_{mi}$ ,  $R_{oi}$ , and  $C_{oi}$  are the i-th stage transconductance, output resistance and output capacitance. Specifically, the input-stage transconductance is  $g_{m1}=g_{mM1}=g_{mM2}$  and the output transconductance is  $g_{m2}=g_{mM11}+g_{mM12}$ .

<sup>&</sup>lt;sup>i</sup> More precisely, the term  $g_{mM12}$  is attenuated by the capacitor divider generated by the QFG, as  $g'_{mM12} = g_{mM12}C_{bat}/(C_{bat} + C_{GS12} + C_{GB12})$ .

Fig. 1. Schematic of the two stage folded-cascode class-AB OTA.

Fig. 2. Simplified small-signal equivalent circuit of the OTA

$C_L$  is the load capacitor that also accounts for  $C_{o2}$ . The frequency compensation branch is implemented by the Miller capacitor  $C_C$  in series with the nulling resistor  $R_C$ .

Evaluation of the transfer function  $V_{out}/V_{in}$  through conventional analysis gives the expression of the DC gain, which is

$$A_o = g_{m1} R_{o1} g_{m2} R_{o2} \tag{1}$$

Moreover, the transfer function includes three (real and negative) poles and one zero. Their expressions are summarized in (2)-(5), where  $\omega_{p1}$  is the dominant pole frequency and  $\omega_{p2}$  and  $\omega_{p3}$  the first and second non-dominant pole frequency, respectively, being usually  $C_L >> C_{o1}$ .

$$\omega_{p1} \approx \frac{1}{R_{o1}g_{m2}R_{o2}C_C} \tag{2}$$

$$\omega_{p2} \approx \frac{g_{m2}}{C_I} \tag{3}$$

$$\omega_{p3} \approx \frac{1}{R_C C_{o1}} \tag{4}$$

$$\omega_z \approx \frac{1}{(R_C - 1/g_{m2})C_C} \tag{5}$$

The expression of the gain-bandwidth product is obtained by multiplying (1) and (2),

$$\omega_{GBW} = A_o \omega_{p1} \approx \frac{g_{m1}}{C_C} \tag{6}$$

which is a key parameter that approximates the unity-gain frequency under dominant pole behavior (i.e.,  $\omega_{p2}>\omega_{GBW}$ ).

The value of  $R_C$ , which modifies the zero frequency in (5), can be set by following two approaches. The first one nullifies the zero moving it towards ideally infinite frequency. This method is called Miller compensation with nulling resistor (MCNR) [24], [25]. The second one moves the zero to the left half plane in order to cancel out the non-dominant pole and is referred to as Miller compensation with pole-zero cancellation (MCPZC) [26]. This latter method is more efficient because it

enhances the phase margin and settling time without additional power consumption and increase in circuit complexity. Its drawback is that it is based on an inherently inaccurate polezero cancellation. Note that the MCPZC leaves the third pole as the non-dominant one and can allow a lower compensation capacitance to be exploited, compared to the MCNR method.

As a result, following the conventional MCNR design strategy, the value of resistor  $R_C$  is set as given by (7a) in order to nullify the denominator of (5). Considering that the phase margin  $\phi$  is implicitly given by  $\tan \phi \approx \omega_{p2}/\omega_{GBW}$ , we also find the expression of  $C_C$  reported in (7b). Similarly, equations (8a) and (8b) are found by following the MCPZC approach, as discussed in [27].

MCNR

$$\begin{cases} R_C = \frac{1}{g_{m2}} \\ C_C = \frac{g_{m1}}{g_{m2}} C_L \tan \phi \end{cases}$$

(7a)

MCPZC

$$\begin{cases} R_{C} = \frac{C_{L} + C_{C}}{g_{m2}C_{C}} \\ C_{C} = \frac{g_{m1}}{g_{m2}} \left( 1 + \sqrt{1 + 4\frac{C_{L}}{C_{ol}} \frac{g_{m2}}{g_{m1} \tan \phi}} \right) C_{ol} \frac{\tan \phi}{2} \end{cases}$$

(8a)

In subthreshold the MOS transconductance is given by the ratio of the DC drain current to the thermal voltage,  $g_m=I_D/nV_t$ . Consequently, (7b) and (8b) can be rewritten as a function of current ratio  $x=I_1/I_2$ , where we remind that  $I_1$  and  $I_2$  are defined in Fig. 1. At this purpose, since  $g_{m2}=g_{mM11}+g_{mM12}$  and hence  $g_{m2}=2I_2/nV_t$ , we can rewrite (7b) and (8b), respectively for MCNR and MCPZC, as

$$C_{C_{-MCNR}} = \frac{I_1}{2I_2} C_L \tan \phi = \frac{1}{2} x C_L \tan \phi$$

(9a)

$$C_{C_{\_MCPZC}} = \frac{I_1}{2I_2} \left( 1 + \sqrt{1 + 4\frac{C_L}{C_{o1}} \frac{2I_2}{I_1 \tan \phi}} \right) C_{o1} \frac{\tan \phi}{2}$$

$$= \frac{x}{4} \left( 1 + \sqrt{1 + \frac{C_L}{C_{o1}} \frac{8}{x \tan \phi}} \right) C_{o1} \tan \phi$$

(9b)

Regarding  $C_{o1}$ , an accurate model is required. In subthreshold, the three main transistor intrinsic parasitic capacitances ( $C_{GS}$ ,  $C_{GD}$  and  $C_{GB}$ ) are in the same order of magnitude. Moreover,  $C_{GB} > (C_{GS} \approx C_{GD})$ . This is different from strong inversion, in which the assumption  $C_{GS} >> C_{GB} > C_{GD}$  is adopted.

An approximated expression of  $C_{o1}$  is then given by (10), where the sub-caption number is related to the associated MOS transistor in Fig. 1.

$$C_{o1} \approx C_{GD6} + C_{DB6} + C_{DB8} + C_{GS11} + C_{GB11} + C_{bat} \frac{C_{GS12} + C_{GB12}}{C_{bat} + C_{GS12} + C_{GB12}}$$

(10)

From the above expression, it is worth noting that the floating battery loads the internal high-impedance node.

### B. Optimized Design

Consider now the total DC current dissipation of the OTA, which can be also expressed in terms of  $I_2$  and current ratio  $x=I_1/I_2$

$$I_T=2I_1+aI_1+I_2=(2+a)I_1+I_2=[(2+a)x+1]I_2$$

(11) where  $a$  is the ratio of the bias current in  $M_7-M_{10}$  to  $I_1$ , as depicted in Fig. 1. Using (7b), (8b) and (11) we can evaluate the gain-bandwidth product for MCNR and MCPZC compensation approaches. For the MCNR technique we get

$$\omega_{GBW\_MCNR} = \frac{g_{m1}}{C_C} = \frac{g_{m1}}{\frac{g_{m1}}{g_{m2}} C_L \tan \phi} = \frac{2I_2}{nV_t C_L \tan \phi}$$

$$= \frac{2I_T}{nV_t C_L \tan \phi} \frac{1}{(2+a)x+1}$$

(12)

which increases with  $I_2$ , or equivalently it tends to infinite for x=0, meaning that no optimization can be provided for a given set of  $I_T$ ,  $C_L$  and  $\phi$ . For the MCPZC technique we get

$$\omega_{GBW\_MCPZC} = \frac{g_{m2}}{\left(1 + \sqrt{1 + 4\frac{C_L}{C_{o1}}\frac{g_{m2}}{g_{m1}\tan\phi}}\right)C_{o1}\frac{\tan\phi}{2}}$$

$$= \frac{4I_T}{nV_tC_{o1}\tan\phi} \frac{1}{\left[(2+a)x + 1\left(1 + \sqrt{1 + 8\frac{C_L}{C_{o1}\tan\phi}\frac{1}{x}}\right)\right]}$$

(13)

It is shown in the Appendix that (13) has a maximum in  $x_M$  whose approximated expression is found in (A5), also rewritten below for convenience

$$x_M \approx \frac{1}{2+a} \tag{14}$$

Given  $I_T$ ,  $C_L$  and  $\phi$ , (14) states that the gain-bandwidth product is maximized for  $I_2\approx (2+a)I_1$ , yielding

$$\omega_{GBW\_MCPZC} = \frac{2I_T}{nV_t C_{o1} \tan \phi} \frac{1}{\left(1 + \sqrt{1 + 8(2 + a)\frac{C_L}{C_{o1} \tan \phi}}\right)}$$

(15)

In our design we will set for simplicity a=2, condition that equalizes the positive and negative internal slew rate, SR, (the currents charging and discharging  $C_C$  have the same magnitude equal to  $2I_1$ , so that  $SR=2I_1/C_c$ ). Of course, 0<a<2 can in principle be chosen to further reduce DC current consumption. As a result, being a=2 and considering (14), we get that  $I_2=4I_1$  would be the optimal setting for a given total current budget and, we remark, for this specific OTA topology. Moreover, it is also worth noting that (6) in subthreshold becomes

$$\omega_{GBW} = \frac{I_1}{nV_t C_C} = \frac{1}{2} \cdot \frac{SR_+}{nV_t} \tag{16}$$

hence, optimization of  $\omega_{GBW}$  leads also to an optimal internal SR, which in a class-AB OTA is the limiting parameter with respect to the external SR [24], [25].

Let us now analyze further the implication of this optimization method by considering that it leads from (11) to  $I_1=I_T/(2a+4)$ . In certain circumstances, this value of  $I_1$  could be too small. For instance,  $I_1$  could not meet additional specifications such as the equivalent input noise. In this case, to keep constant  $I_T$ , we should decrease  $I_2$  from its optimum value and increase  $I_1$ , at the expense of a reduction of  $\omega_{GBW}$ . Fortunately, as it can be inferred from Fig. A1 in the Appendix, selecting  $I_2 < 4I_1$  up to  $I_2 = I_1$  (i.e., x=1) reduces  $\omega_{GBW}$  by no more than 30%, compared to its theoretical maximum. This means that a good trade-off between the OTA gain-bandwidth product and the equivalent input noise voltage performance is achieved by setting  $I_2=I_1$ . Assuming a=2, from (11) this choice means that  $I_1=I_T/5$  yielding to a 60% increase of  $I_1$  from  $I_T/8$ , in the optimum  $\omega_{GBW}$  condition. In conclusion, we will purposely set a=2and  $I_2=I_1$  in our design.

### III. EXPERIMENTAL RESULTS

A test chip prototype of the amplifier in Fig. 1 was fabricated using the AMI 0.5- $\mu$ m n-well CMOS process, with nMOS (pMOS) threshold voltage of 0.67 V (-0.97 V). The subthreshold slope for both devices was approximately 1.5. As design constraints, the supply voltage was set to 1.6 V and the load capacitor  $C_L$  was set externally to 40 pF. The target phase margin was  $\phi$ =60°. To achieve subthreshold operation,  $2I_1$  was set to 300 nA and the same value was set as DC current of transistors M<sub>3</sub> and M<sub>4</sub> (i.e., as already stated we set a=2). The second stage DC current  $I_2$  was set equal to  $I_2$ =150 nA. The total bias current from (11) is therefore equal to 750 nA.

The aspect ratios (in  $\mu m/\mu m$ ) of transistors are 7.5/1(x8) for  $M_0$ ; 15/0.6(x8) for  $M_{1,2,b4}$ ; 7.5/1(x4) for  $M_{3,4,b3}$ ; 2.55/1(x2) for  $M_{5-8}$ ; 3.75/1(x4) for  $M_{9,10}$ ; 7.5/1(x2) for  $M_{11,12,b2,b6}$ ; 15/0.6(x4) for  $M_{b1}$ ; 4.95/1(x2) for  $M_{b5}$ . Note how the aspect ratio of differential pair has been increased to improve the input signal swing as well as noise performance. For the QFG implementation,  $C_{bat}$ is 1 pF and M<sub>bat</sub> is 1.5/1 according to [21]. Regarding frequency compensation,  $C_C$  and  $R_C$  are set equal to 1.4 pF and 4.1 M $\Omega$ , respectively, which can be obtained by substituting the DC conditions in equations 8a and 8b. Because of the high-valued resistor required by MCPZC, R<sub>c</sub> was implemented by using a MOS transistor in ohmic region. Finally,  $C_{o1}$  is 50 fF. Evaluating the ratio  $C_L/C_{o1}$  we found that parameter b defined in the Appendix is greater than 3600. The maximum GBW is from (15) 458 kHz and a reduction of about 20 % is caused by selecting  $I_2=I_1$ . The die photograph of the OTA is shown in Fig. 3, whose occupied area is 0.0088 mm<sup>2</sup>.

87.0-um

Fig. 3. Chip microphotograph.

The simulated AC response of the OTA is reported in Fig. 4 while Fig. 5 shows the measured transient response. A reduction of the measured negative slew rate is observed as compared to the simulated value, which can be justified by introducing additional parasitic capacitors not considered in simulations. Indeed, transconductance of  $M_{12}$  is attenuated by a capacitor division of  $\beta = C_{bat}/(C_{bat} + C_{QFG})$  where  $C_{QFG} = C_{GS12} + C_{GB12} + C_{GD12}(1 + g_{m12}r_{o12}) + C_{bat,subs} + C_{Mbat}$  in which  $C_{bat,subs}$  is the bottomplate parasitic capacitance of  $C_{bat}$ , and  $C_{Mbat}$  is the parasitic capacitance of pseudo-resistor  $M_{bat}$  at the node that connects it to  $C_{bat}$ . In addition, parametric process variations could also reduce the transconductance of  $M_{12}$ , leading to a degradation in the negative slew rate.

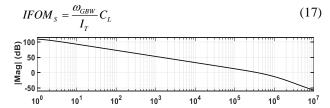

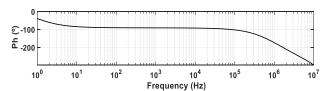

Table I summarizes the main performance parameters. A comparison with other amplifiers operating in subthreshold is reported in Table II. Note that the total quiescent current is higher than 750 nA since it includes the current dissipated by the biasing circuit. Performance comparison is carried out considering two widely adopted figures of merit [9], [12], [18]-[20]

Fig. 4. Simulated AC response.

0.4

0.2

0.2

0.4

0.01

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.10

0.

Fig. 5. Measured transient response.

TABLE I - MEASURED PERFORMANCE

| Parameter                          | Value             |  |  |  |

|------------------------------------|-------------------|--|--|--|

| Supply voltage (V)                 | 1.6V              |  |  |  |

| Total quiescent current (µA)       | 0.98              |  |  |  |

| GBW (kHz) †                        | 370.5             |  |  |  |

| DC gain (dB) †                     | 104.8             |  |  |  |

| Phase margin (°) †                 | 53.5              |  |  |  |

| Pos./Neg. settling time 1% (μs)    | 10.7/12           |  |  |  |

| Pos./Neg. Slew rate (V/ms)         | 148.8/-43.5       |  |  |  |

| CMRR (dB) †                        | 90.1              |  |  |  |

| PSRR+/PSRR- (dB) †                 | 72.3/75.0         |  |  |  |

| Eq. Input Noise $(nV/\sqrt{Hz})$ † | 175.8 @ 370.5 kHz |  |  |  |

| Area (mm <sup>2</sup> )            | 0.0088            |  |  |  |

†Simulated

TABLE II -PERFORMANCE COMPARISON

| Parameter                     | [11]   | [12]   | [16]  | [17]  | [18]  | [19]  | [20]   | This<br>work |

|-------------------------------|--------|--------|-------|-------|-------|-------|--------|--------------|

| Tech. (µm)                    | 0.18   | 0.065  | 0.18  | 0.18  | 0.18  | 0.18  | 0.35   | 0.5          |

| Area (mm <sup>2</sup> )       | 0.0082 | 0.002  | 0.017 | 0.057 | 0.036 | 0.057 | 0.0044 | 0.0088       |

| Sup. voltage(V)               | 0.3    | 0.25   | 0.5   | 0.8   | 0.5   | 0.5   | 1      | 1.6          |

| $C_L$ (pF)                    | 20     | 15     | 20    | 8     | 40    | 30    | 200    | 40           |

| DC Gain (dB)                  | 63     | 70     | 62    | 51    | 77    | 70    | 129    | 105          |

| Power (µW)                    | 0.0168 | 0.026  | 75    | 1.2   | 0.07  | 0.075 | 0.195  | 1.568        |

| GBW (kHz)                     | 0.0028 | 0.0095 | 10000 | 57    | 4     | 8     | 20     | 307.5        |

| PM (°)                        | 61     | 88     | 60    | 60    | 56    | 55    | 52     | 54           |

| $SR^{\dagger}(V/\mu s)$       | 0.0071 | 0.002  | 2     | 0.14  | 0.002 | 0.003 | 0.005  | 0.096        |

| CMRR (dB)                     | 72     | 63     | 65    | 65    | 55    |       | 70     | 90           |

| PSRR (dB)                     | 62     | 38     | 43    |       | 52    |       | 184    | 72           |

| No. of stages                 | 2      | 3      | 2     | 1     | 2     | 2     | 3      | 2            |

| $IFOM_S$<br>(kHz·pF/ $\mu$ A) | 1      | 1.37   | 1.33  | 0.30  | 1.14  | 3.60  | 20.51  | 12.55        |

| $IFOM_L$<br>(V/μs·pF/μA)      | 2.54   | 0.29   | 0.27  | 0.75  | 0.57  | 0.60  | 5.13   | 3.92         |

†average value

$$IFOM_L = \frac{SR}{I_T}C_L \tag{18}$$

As compared to other OTAs, the proposed amplifier exhibits the second highest values of  $IFOM_S$  and  $IFOM_L$ , being only the three-stage OTA in [20] the best in terms of both small and large-signal performance.

### IV. CONCLUSIONS

A methodology to design subthreshold two-stage CMOS OTAs with optimized GBW to DC-current ratio is presented. The optimization process relates the first and second stage bias currents with the compensation capacitors as well as other design constraints such as load capacitance, output first stage capacitance and phase margin. Through this ratio, GBW is maximized for a given current budget, increasing both FOMs and FOML. The proposal has been verified in class-AB OTA implemented with the QFG technique, improving the small and large-signal performance with no additional power increment. In order to verify the whole guidelines, a 0.5-µm test chip prototype has been simulated and fabricated, demonstrating the proposed methodology and exhibiting outstanding results.

## **APPENDIX**

The maximum of (13) is found by minimizing the function f(x) in (A1), in which we define for simplicity parameter  $b=8C_L/(C_{o1}\tan\phi)$ . Note that b is much greater than the unity, being  $C_L>>C_{o1}$ .

$$f(x) = [(2+a)x+1](1+\sqrt{1+\frac{b}{x}})$$

(A1)

The derivative of (A1) with respect to x is

$$f'(x) = \frac{2(2+a)x^2\sqrt{1+\frac{b}{x}}\left(1+\sqrt{1+\frac{b}{x}}\right) - b\left[1+(2+a)x\right]}{2x^2\sqrt{1+\frac{b}{x}}}$$

(A2)

Setting the derivative to zero and being x>0, we get

$$2(2+a)x^{2}\left(\sqrt{1+\frac{b}{x}}+1+\frac{b}{x}\right)-(2+a)bx-b=0$$

(A3)

where we can neglect the squared term in the round brackets, being its argument much greater than the unity. Moreover, considering that b/x>>1, we get

$$(2+a)bx - b \approx 0 \tag{A4}$$

Therefore, the maximum of (13), i.e. the minimum of (A1), occurs for

$$x_M \approx \frac{1}{2+a} \tag{A5}$$

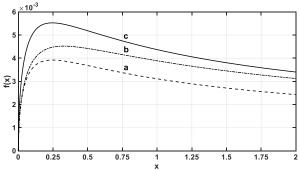

As a further illustrative proof of this result, we plot 1/f(x) versus x in three selected example cases, namely, for a=2 with b equal to 2000 and 4000, and for a=1 with b=4000. In particular, we see that the three diagrams are relatively flat near their maximum, which occurs at  $x_M=1/4$  for a=2 in curves a and b, and at  $x_M=1/3$  for a=1 in curve c, as anticipated by (A5).

Fig. A1. Plot of 1/f(x) versus x for: a) a=1, b=4000, b) a=2, b=4000, and c) a=2, b=2000.

The almost flat behavior of the curves around the maximum indicates that  $x>x_M$  can be chosen without strongly reducing the gain-bandwidth product. For example, selecting  $I_2=I_1$  (i.e., x=1) causes a  $\omega_{GBW}$  reduction of around 20% in the cases of curves a and b, and of around 30% in the case of curve c.

### REFERENCES

- A.P. Chandrakasan, et al., "Ultralow-Power Electronics for Biomedical Applications," Annu. Rev. Biomed. Eng., vol. 10, no. 1, pp. 247

–274, 2008.

- [2] A. Tabesh and L. G. Fréchette, "A Low-Power Stand-Alone Adaptive Circuit for Harvesting Energy From a Piezoelectric Micropower Generator," *IEEE Trans. Ind. Elec.*, vol. 27, no. 3, pp. 740–749, Mar. 2010.

- [3] M. Alioto (Ed.), Enabling the Internet of Things from Integrated Circuits to Integrated Systems, Springer 2017.

- [4] C.S. Abella et al., "Autonomous Energy-efficient Wireless Sensor Network Platform for Home/Office Automation", *IEEE Sensors Journal*, Vol. 19, No 9, pp. 3501-3512, May 2019.

- 5] E. Vittoz and J. Fellrath, "CMOS analog integrated circuits based on subthreshold operations," *IEEE J. Solid-State Cir.*, vol. 12, no. 3, pp. 224–231, Jun. 1977.

- [6] L. Lv, et al., "Inverter-Based Subthreshold Amplifier Techniques and Their Application in 0.3-V DS -Modulators," *IEEE J. Solid-State Cir.*, vol. 54, no. 5, pp. 1436-1445, May 2019.

- [7] F. Michel, M.S.J. Steyaert, "A 250 mV 7.5 µW 61 dB SNDR SC ΔΣ modulator using near-threshold-voltage-biased inverter amplifiers in 130 nm CMOS," *IEEE J. Solid-State Cir.* vol. 47, no. 3, pp. 709-721, Mar. 2012.

- [8] B.J. Blalock, et al., "Design 1-V Op Amps Using Standard Digital CMOS Technology," *IEEE Trans. Circ. Syst. II.*, vol. 45, no. 7, pp. 769-780, Jul. 1998.

- [9] L. Zuo and S. K. Islam, "Low-Voltage Bulk-Driven Operational Amplifier With Improved Transconductance," *IEEE Trans. Circ. Syst I: Reg. Pap.*, vol. 60, no. 8, pp. 2084–2091, Aug. 2013.

- [10] E. Cabrera-Bernal, et al., "0.7-V Three-Stage Class-AB CMOS Operational Transconductance Amplifier," *IEEE Trans. Circ. Syst I*, vol. 63, no. 11, pp. 1807-1815, Nov. 2016.

- [11] T. Kulej and F. Khateb, 'Design and implementation of sub 0.5-V OTAs in 0.18µm CMOS', Int. J. Circuit Theor. Appl., vol. 46, no. 6, pp. 1129–1143, Jun. 2018.

- [12] K.-C. Woo and B.-D. Yang, 'A 0.25-V Rail-to-Rail Three-Stage OTA With an Enhanced DC Gain', *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 67, no. 7, pp. 1179–1183, Jul. 2020

- [13] J. Li, D. Paik, S. Lee, M. Miyahara, and A. Matsuzawa, "An ultralow-voltage 160 MS/s 7 bit interpolated pipeline ADC using dynamic amplifiers," *IEEE J. Solid-State Cir.*, vol. 50, no. 6, pp. 1399–1411, Jun. 2015.

- [14] Y. Lim and M. P. Flynn, "A 100 MS/s, 10.5 bit, 2.46 mW comparatorless pipeline ADC using self-biased ring amplifiers," *IEEE J. Solid-State Cir.*, vol. 50, no. 10, pp. 2331–2341, Oct. 2015.

- [15] T. Stockstad and H. Yoshizawa, "A 0.9-V 0.5-um rail-to-rail CMOS operational amplifier," *IEEE J. Solid-State Cir.*, vol. 37, no. 3, pp. 286–292, Mar. 2002.

- [16] S. Chatterjee, Y. Tsividis, and P. Kinget, "0.5-V analog circuit techniques and their application in OTA and filter design," *IEEE J. Solid-State Cir.*, vol. 40, no. 12, pp. 2373–2387, Dec. 2005.

- [17] M.R. Valero Bernal, et al., "An Ultralow-Power Low-Voltage Class-AB Fully Differential OpAmp for Long-Life Autonomous Portable Equipment," *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 59, no. 10, pp. 643–647, Oct. 2012.

- [18] Z. Qin, et al. "0.5-V 70-nW Rail-to-Rail Operational Amplifier Using a Cross-Coupled Output Stage," *IEEE Trans. Circuits Syst. II Express Briefs*, vol. 63, no. 11, pp. 1009–1013, Nov. 2016.

- [19] L. Magnelli, et al., "Design of a 75-nW, 0.5-V subthreshold complementary metaloxide-semiconductor operational amplifier," *Int. J. Circuit Theor. Appl.*, vol. 42, no. 9, pp. 967–977, Sep. 2014.

- [20] A.D. Grasso, et al., "Design Methodology of Subthreshold Three-Stage CMOS OTAs Suitable for Ultra-Low-Power Low-Area and High Driving Capability", IEEE Trans. Circ. Syst. I, vol. 62, no. 6, pp. 1453–1462, Jun. 2015.

- [21] J. Ramirez-Angulo, et al., "Very low-voltage analog signal processing based on quasi-floating gate transistors," *IEEE J. Solid-State Cir.*, vol. 39, no. 3, pp. 434-442, Mar. 2004.

- [22] A.J. Lopez-Martin, et al., "Low-Voltage Super class AB CMOS OTA cells with very high slew rate and power efficiency," *IEEE J. Solid-State Cir.*, vol. 40, no. 5, pp. 1068-1077, May 2005.

- [23] J. Ramirez-Angulo, et al.,"A free but efficient low-voltage class-AB two-stage operational amplifier," *IEEE Trans. Circuits Syst. II*, vol. 53, no. 7, pp. 568-571, Jul. 2006

- [24] G. Palmisano, et al., "Design Procedures for Two-Stage CMOS OTAs: A Tutorial," Analog Int. Circ. Sig. Proc., vol. 27, no. 3, pp. 179–189, May 2001.

- [25] G. Palumbo and S. Pennisi, Feedback Amplifiers: Theory and Design, Springer

- [26] W. Black, Jr., D. Allstot, and R. Reed, "A high performance low power CMOS channel filter," *IEEE J. Solid-state Cir.*, vol. SC-15, no. 6, pp. 929-938, Dec. 1980.

- [27] A.D. Grasso, et al., "Comparison of the Frequency Compensation Techniques for CMOS Two-Stage Miller OTAs," *IEEE Trans. Circuits Syst. II*, vol. 55, no. 11, pp. 1099-1103, Nov. 2008.